單精度浮點加法器的FPGA實現

2.2.1 總體設計

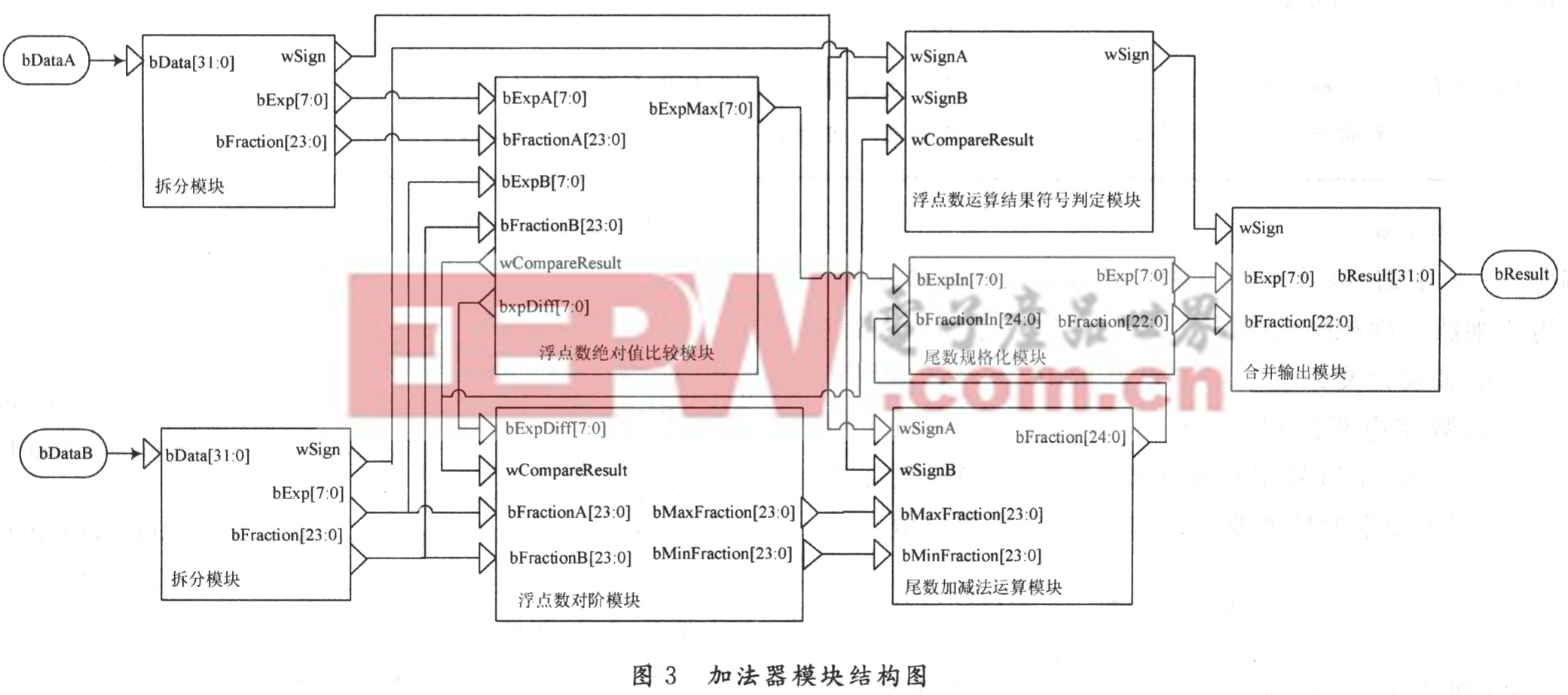

浮點加法器包括兩個浮點數拆分模塊、絕對值比較模塊、浮點數運算結果判定模塊、對階模塊、尾數加減運算模塊、尾數規格化模塊、合并輸出模塊。其中對階模塊包括尾數交換,尾數移位兩個子模塊;尾數加減運算模塊尾數運算符號判定,尾數加減兩個子模塊。兩個浮點數拆分模塊分別將兩個浮點數拆分成符號、階碼、尾數3部分,絕對值比較模塊通過對兩個浮點數的絕對值大小的比較得到大階,階差和絕對值比較結果,大階直接輸出;對階模塊然后實現對小階的尾數進行移位,將小階與大階對齊,并對尾數進行移位;尾數加減運算模塊判定尾數運算符號后,進行尾數運算;尾數規格化模塊對結果完成尾數規格化,同時調整階碼;最后結合浮點數運算結果判定模塊的符號輸出,經過合并輸出模塊,得到結果輸出。總體設計框圖如圖3所示。本文引用地址:http://www.104case.com/article/192020.htm

2.2.2 各模塊設計實現說明

(1)拆分模塊。該模塊將輸入的浮點數拆分成符號位、價碼、尾數3部分。符號位信號wSign,指數位信號bExp[7:0],尾數位信號bFraction[23:0]。

(2)浮點數絕對值比較模塊。該模塊通過對輸入浮點的階碼及尾數的比較,相應得出wCompareResult,bExpDiff,bExpMax三種信號輸出。當bExpA≥bEx-pB時:wCompareResult=1,bExpDiff=bExpA-bEx-pB,bExpMax=bExp;當bExpAbExpB時:wCom-pareResult=0,bExpDiff=bExpB-bExpA,bExpMax=bExpB。

(3)浮點數運算結果符號判定模塊。浮點數符號運算結果判別模塊通過操作數bDataA,bDataB符號位及wCompareResult信號的輸入判定運算結果數的輸出。

(4)浮點數對階模塊。對階模塊根據wCompare-Result的結果對輸入的操作數尾數bFractionA和bFractionB進行操作。當wCompareResult=1時,對bFractionB進行右移位,移位量為bExpDiff,并且將移位后的結果作為bMinFraction輸出,將bFractionA作為bMaxFraction直接輸出;反之對bFractionA進行右移位,移位量為bExpDiff,并且將移位后的結果作為bMinFraction輸出,將bFractionB作為bMaxFraction直接輸出。

(5)浮點數對階模塊。此模塊實現對階后的尾數的加減運算,然后輸出結果尾數的值。當wSignA,wSignB同號時,尾數bMaxFraction與bMinFraction相加的結果作為bFraction輸出;當wSignA,wSignB異號時,尾數bMaxFraction與bMinFraction相減的結果作為bFraction輸出。

(6)尾數規格化模塊。尾數bFractionIn[24:0]通過判定從左邊第一次不為0的位后,將此位數左移到第一位隱藏位,相應添加尾數補0,共計24位。同時,將階碼調整,再隱藏隱藏位,調整后的階碼和尾數以bExp,bFraction輸出。

(7)合并輸出模塊。將浮點數運算結果符號判定模塊的輸出信號wSign與尾數規格化模塊的輸出信號bExp,bFraction合并,得到輸出結果。

3 結 語

介紹一種在FPGA上實現的單精度浮點加法運算器,運算器算法的實現考慮了FPGA器件本身的特點,算法處理流程的拆分和模塊的拆分,便于流水設計的實現。該加法器在作者參與設計的多款CPCI總線圖形控制器圖形加速子系統上得到實際的應用和檢驗,在處理速度方面表現出很強的適用性。

評論