- 多加數的加法器是FPGA的一個比較常見的應用。仿真對比了其三種實現方案的性能和所消耗資源,得出進位保留加法陣列是首選方案。針對進位保留加法陣列實現的復雜性給出了一個加法陣列的HDL代碼生成器,極大地簡化了加法陣列的設計工作。

- 關鍵字:

HDL代碼生成器 加法器 FPGA

- 加法器 :

加法器是為了實現加法的。

即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

對于1位的二進制加法,相關的有五個的量:1,被加數A,2,被加數B,3,前一位的進位CIN,4,此位二數相加的和S,5,此位二數相加產生的進位COUT。前三個量為輸入量,后兩個量為輸出量,五個量均為1位。

對于32位的二進制加法,相關的也有五個量

- 關鍵字:

加法器

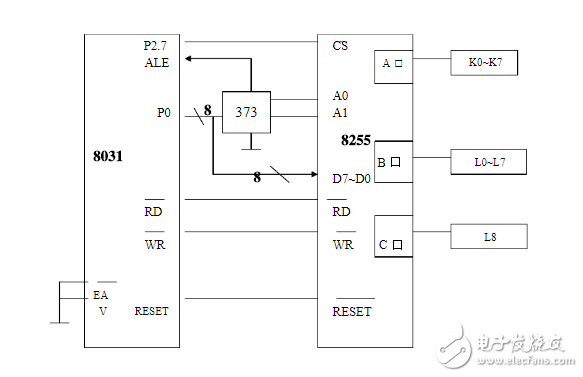

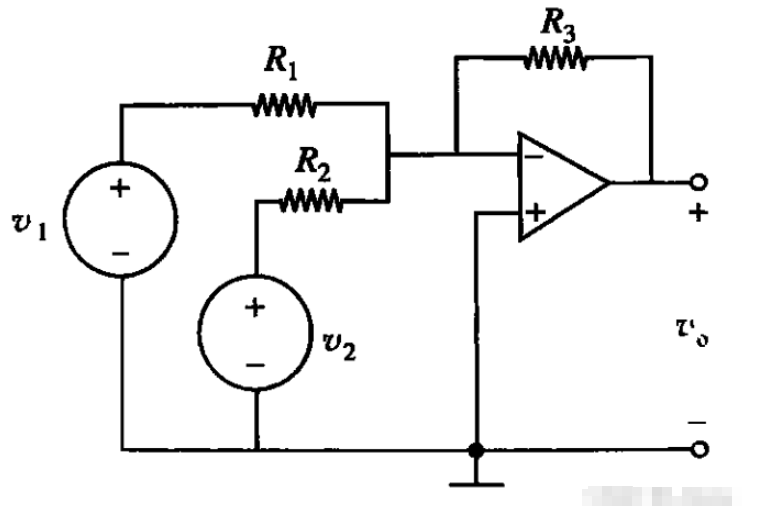

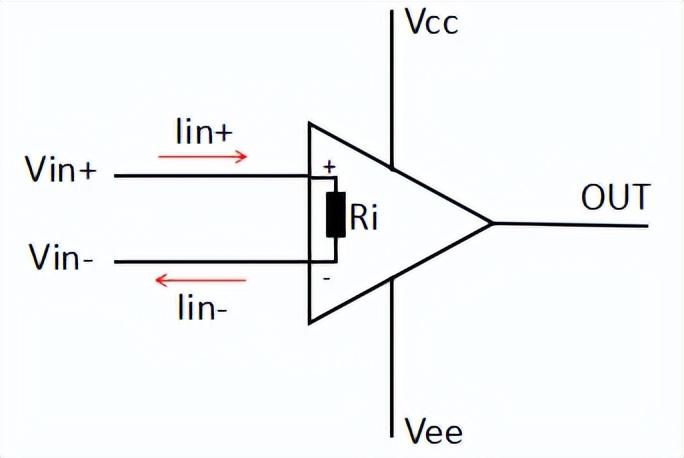

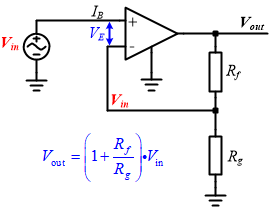

- 隨著FPGA的功能日益強大和完善,FPGA在項目中的應用也越來越廣泛,其技術關鍵在于控制日益廣泛而豐富的外圍器件。本文以Flash存儲器件為FPGA的外圍,敘述了FPGA中SPI總線接口的Flash驅動模塊的設計,其接口基本符合Avalon總線的規范要求,并且通過實際的讀寫操作驗證。傳統反相運算放大器的加法器配置利用反相輸入端的低阻抗節點(虛擬地)的特性而實現。加法電路非常直觀且易于分析和使用,不過它確實存在某些限制。面對常規或復雜電路功能時,運算放大器非常好用,可提供很多實用且

- 關鍵字:

DAI 加法器 放大器 電路

- 摘要:浮點運算器的核心運算部件是浮點加法器,它是實現浮點指令各種運算的基礎,其設計優化對于提高浮點運算的速度和精度相當關鍵。文章從浮點加法器算法和電路實現的角度給出設計方法,通過VHDL語言在OuartusII中進

- 關鍵字:

FPU 加法器

- 隨著儀表放大器價格的逐步下滑,它們可以為傳統上采用運算放大器的應用提供更高的性能。圖1中的運放加法器有一些缺點。首先,輸入端為中低輸入阻抗,這是由每個信號的輸入電阻所決定的。當驅動信號源阻抗較大,或需要

- 關鍵字:

儀表放大器 性能 加法器

- 本工程設計完全符合IP核設計的規范流程,而且完成了Verilog HDL建模、功能仿真、綜合、時序仿真等IP核設計的整個過程,電路功能正確。實際上,本系統在布局布線后,其系統的最高時鐘頻率可達80MHz。雖然使用浮點數會導致舍入誤差,但這種誤差很小,可以忽略。實踐證明,本工程利用流水線結構,方便地實現了高速、連續、大數據量浮點數的加法運算,而且設計結構合理,性能優異,可以應用在高速信號處理系統中。

- 關鍵字:

FPGA 流水線 浮點 加法器

- 摘 要:在FPGA上實現單精度浮點加法器的設計,通過分析實數的IEEE 754表示形式和IEEE 754單精度浮點的存儲格式,設計出一種適合在FPGA上實現單精度浮點加法運算的算法處理流程,依據此算法處理流程劃分的各個處理模塊

- 關鍵字:

FPGA 精度 浮點 加法器

- 在數字電路中,常需要進行加、減、乘、除等算術運算,而乘、除和減法運算均可變換為加法運算,故加法運算電路應用十分廣泛。

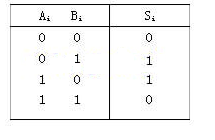

1.半加器

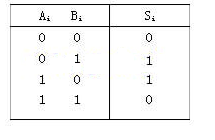

不考慮由低位來的進位,只有本位兩個數相加,稱為半加器。圖1(a)為半加器的方框圖。其中:A、B分別為被加數與加數,作為電路的輸入端;S為兩數相加產生的本位和,它和兩數相加產生的向高位的進位C一起作為電路的輸出。

圖1 半加器框圖、邏輯圖和符號

根據二進制數相加的原則,得到半加器的真值表如表1所列。

表1 半加器的真值表

- 關鍵字:

加法器 邏輯電路

- 高速數字串行加法器及其應用 深圳南山區科技園中興通訊IC開發一部(518057) 鐘信潮上海盛立亞光網絡系統有限公司 薛小剛深圳南山區科技園中興通訊3G開發(518057) 王 誠

摘 要:與傳統加法器相比,數字串行加法器具有工作頻率高、占用資源少、設計靈活等優點。介紹了數字串行加法器的原理,說明了該加法器在FPGA上的實現要點及其在匹配濾波器設計中的應用。 關鍵詞:加法器 位并行 數字串行 FPGA 匹配濾波器

與傳統DSP相比,定制DSP具有速度更高、設計靈活、易于更改

- 關鍵字:

FPGA 加法器 匹配濾波器 數字串行 位并行

加法器介紹

目錄

1 簡介

2 基本方法

3 工作原理

4 類型

5 結構設計

6 邏輯優化

簡介

加法器是為了實現加法的。

即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

對于1位的二進制加法,相 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473