基于單片機和FPGA的網絡數據加密實現

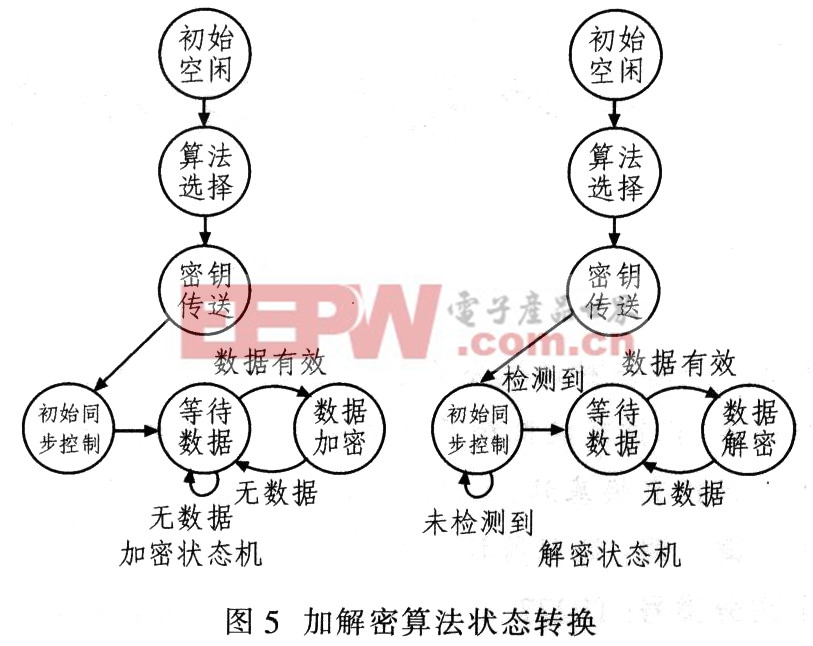

FPGA的模塊控制由兩個獨立的狀態機組成,用于處理加密算法和解密算法,其狀態轉換如圖5所示。本文引用地址:http://www.104case.com/article/192015.htm

系統上電初始化后,由用戶向單片機輸入初始密鑰和算法選擇數據,通過SPI接口送入FPGA,FPGA接收到密鑰后將初始密鑰傳給算法模塊,算法模塊初始化后產生同步Gold碼,并等待數據,當待加密數據有效時,啟動加密算法;當數據無效時,再次進入等待數據狀態。相應地,解密模塊先檢測起始的同步Gold碼,檢測到后,當待解密數據有效時,啟動解密算法,當待解密數據無效時,再次進入等待數據狀態。如此往復,完成數據的加密解密過程。在密鑰傳輸過程中,由于兩種算法所需的初始密鑰位數不同,當使用w7算法時,初始密鑰在送入FPGA中后還需二次擴展達到所需的位數。

4 仿真與分析

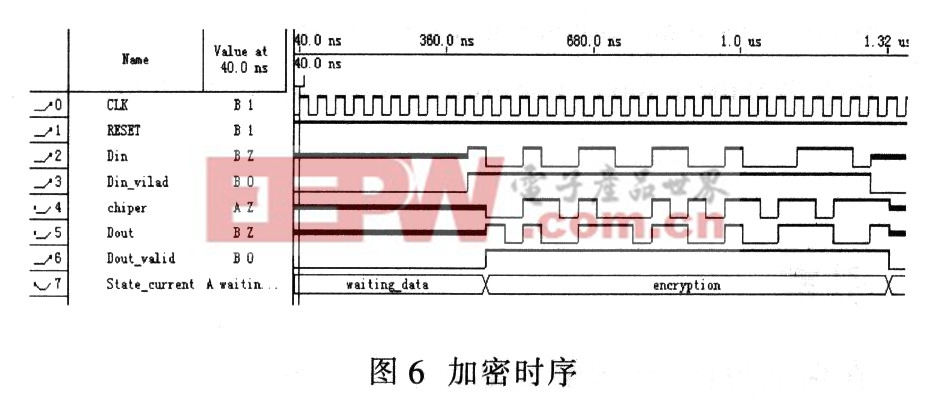

采用QuartuslI 8.0軟件仿真FPGA功能。共用4 865個邏輯單元,1 024 bit的片上存儲位,時序分析得到最大工作頻率為95.79 MHz。仿真加密時序如圖6所示。

5 結論

通過對整個設計的調試驗證,結果滿足設計要求。整個系統具有較高的安全性和保密性,可為要求通信安全的網絡應用提供一種基于硬件的加密方式,基于FPGA的加密算法設計具有很高的靈活性,如果采用更加先進的加密算法,可進一步提高系統的安全性和保密性。

pos機相關文章:pos機原理

評論