基于單片機(jī)和FPGA的網(wǎng)絡(luò)數(shù)據(jù)加密實(shí)現(xiàn)

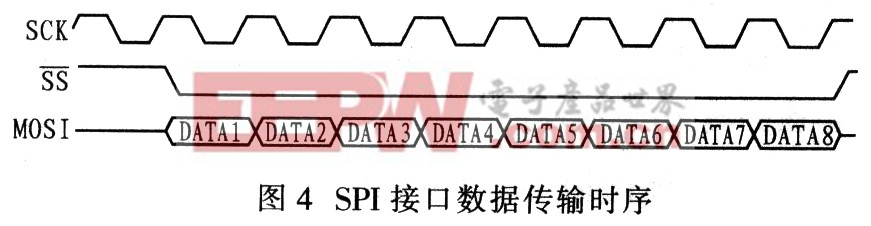

由于TI公司的MSP430系列微處理器平臺(tái)具有低功耗和小體積等特點(diǎn),適合便攜式應(yīng)用場(chǎng)合,所以單片機(jī)采用MSP430系列,并通過SPI接口實(shí)現(xiàn)與FPGA的數(shù)據(jù)通信。單片機(jī)外接一鍵盤,用于輸入初始密鑰。考慮到用戶輸入密鑰位數(shù)不能很多,可設(shè)置簡(jiǎn)短的密鑰,并在單片機(jī)內(nèi)部擴(kuò)展至算法所需的位數(shù),然后通過單片機(jī)SPI接口傳送至FGPA。SPI接口共4條信號(hào)線:串行時(shí)鐘(SCK),主機(jī)輸出/從機(jī)輸入(MOSI),主機(jī)輸入/從機(jī)輸出(MISO),從機(jī)片選(SS)。SPI接口可配置為主或從模式。設(shè)計(jì)配置為主模式。當(dāng)單片機(jī)向FPGA傳輸命令或數(shù)據(jù)時(shí),應(yīng)用SPIO模式。當(dāng)片選信號(hào)丙拉低,在每個(gè)時(shí)鐘(SCK)的上升沿發(fā)送數(shù)據(jù),無需FPGA向單片機(jī)輸人數(shù)據(jù),所以不使用MISO數(shù)據(jù)線。片選信號(hào)SS與FP-CA的RAM的使能相連,控制數(shù)據(jù)讀入。當(dāng)用戶輸人初始密鑰后,經(jīng)過數(shù)據(jù)擴(kuò)展,與算法選擇數(shù)據(jù)通過SPI接口傳送至FPGA。SPI接口時(shí)序如圖4所示。本文引用地址:http://www.104case.com/article/192015.htm

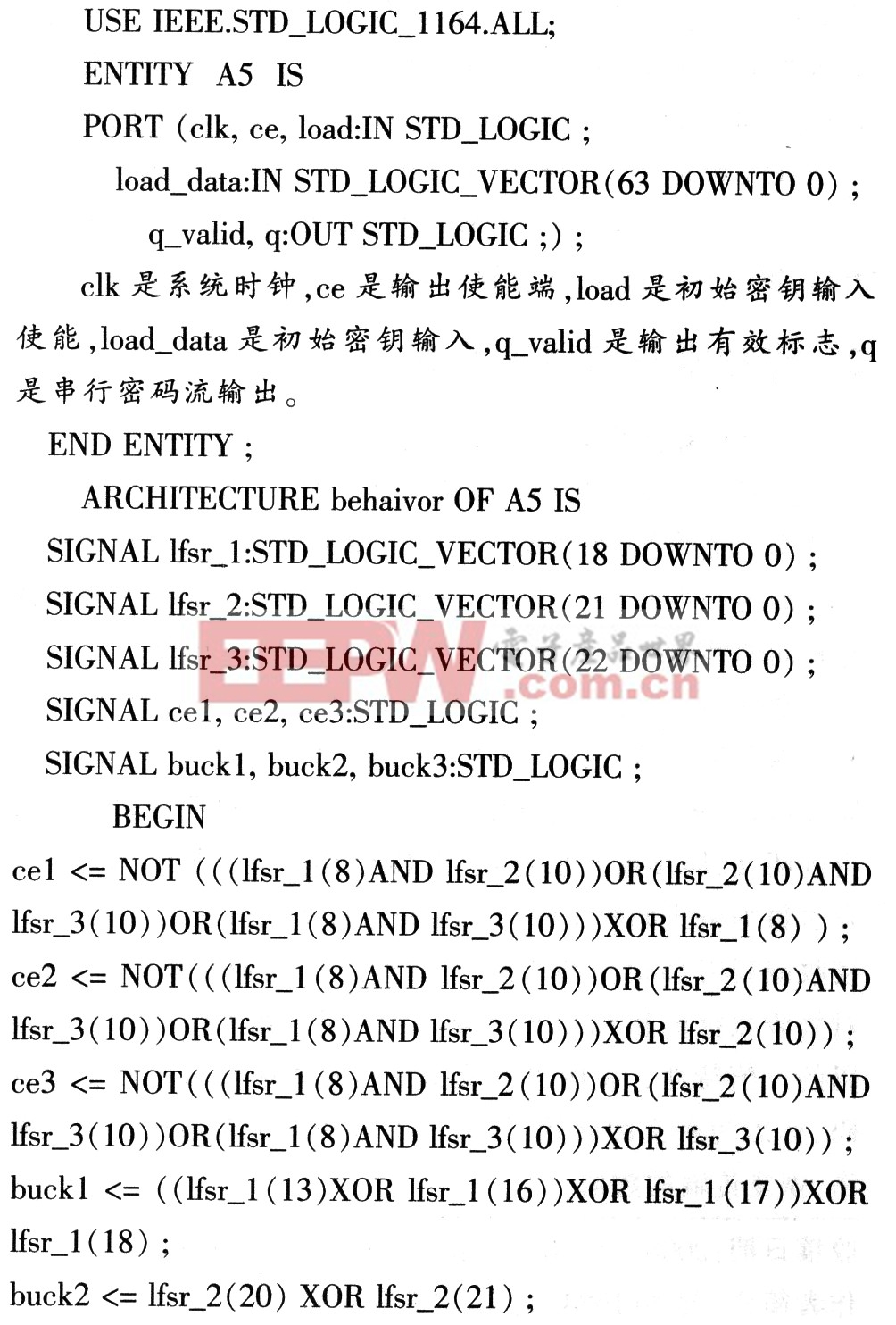

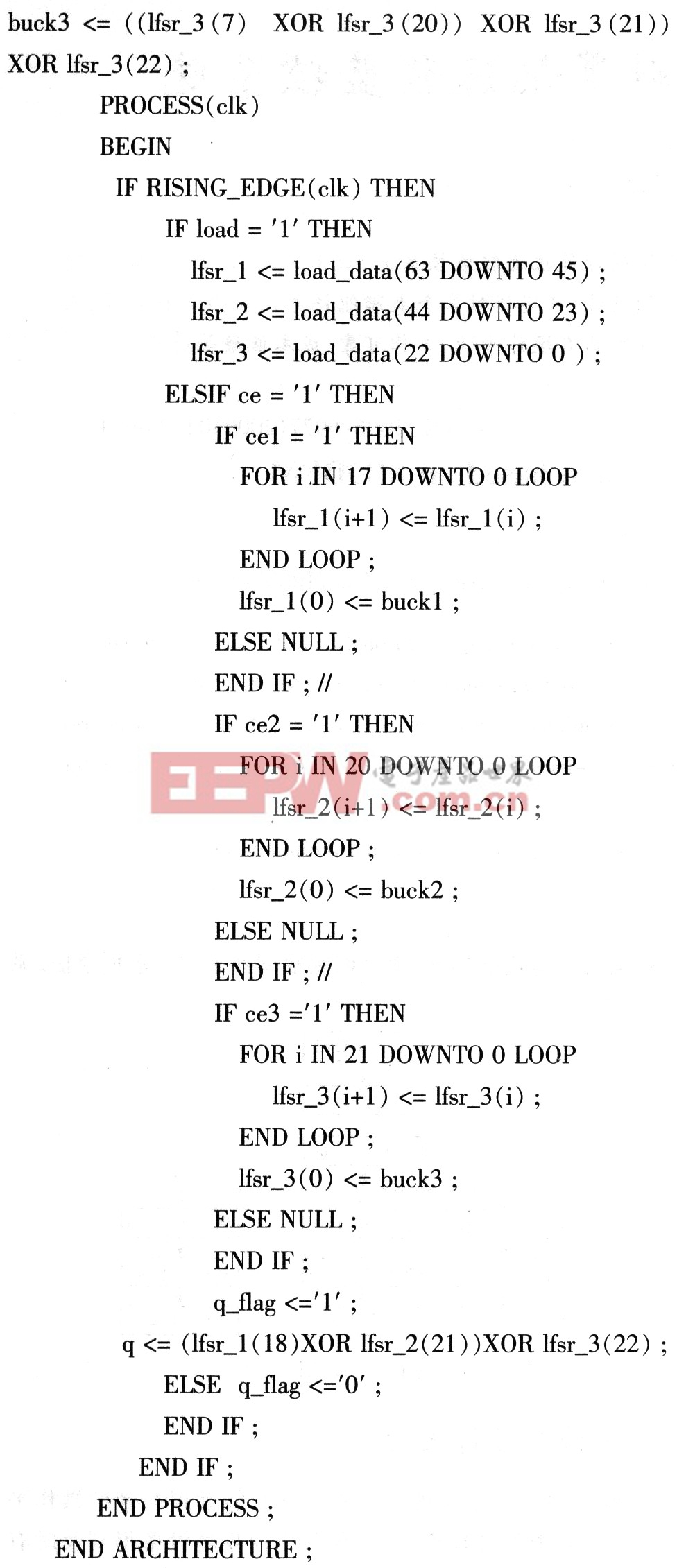

FPGA采用CyeloneII系列中的EP20F256C6,該器件是低成本架構(gòu)FPGA,可提供多達(dá)18 752個(gè)邏輯單元.152個(gè)用戶IO,239 616 bit的存儲(chǔ)位,密度超過CyeloneI FPGA的3倍,完全滿足系統(tǒng)設(shè)計(jì)需要。CycloneII FPGA內(nèi)部的邏輯資源可實(shí)現(xiàn)復(fù)雜應(yīng)用。CyeloneII器件采用的低成本串行配置器件,這種串行配置器件最大可提供64 Mbit的nash存儲(chǔ)器。所以,采用EP20F256C6可高效完成系統(tǒng)核心算法,有效節(jié)約成本。其內(nèi)部算法由VHDL語言編程實(shí)現(xiàn)。主要程序模塊:加解密算法模塊(A5/1和W7)、數(shù)據(jù)存儲(chǔ)模塊、同步產(chǎn)生模塊、同步檢測(cè)模塊。加密和解密各有一套獨(dú)立的模塊集合。其中A5/1算法模塊的VHDL代碼如下:

pos機(jī)相關(guān)文章:pos機(jī)原理

評(píng)論