FPGA布局布線后的仿真波形如圖4、圖5所示。

從仿真結果(圖4,圖5)和ISE 8.2i的綜合報告可知,該校正模塊的最高時鐘頻率達到102.5MHz。

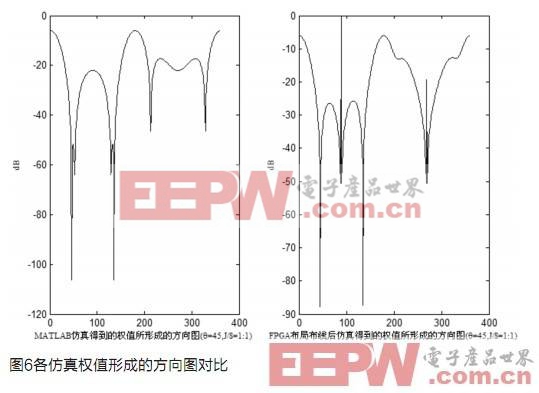

最后,由MATLAB仿真和FPGA布局布線后仿真得到的權值,經過MATLAB仿真形成新的方向圖,如圖6所示,可以看出,兩種方向圖基本一致。因此,基于FPGA的多通道校準同步算法的實現完全符合系統要求。

結語

由于數據時鐘的同步是FPGA 芯片設計實現的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據時鐘的同步有問題。而本文提出了解決這一問題的時鐘同步方法,并在硬件上很好地實現了多通道校準算法,極大提高了系統穩定性。

評論