基于FPGA的多通道校準(zhǔn)算法的同步實(shí)現(xiàn)

FPGA實(shí)現(xiàn)

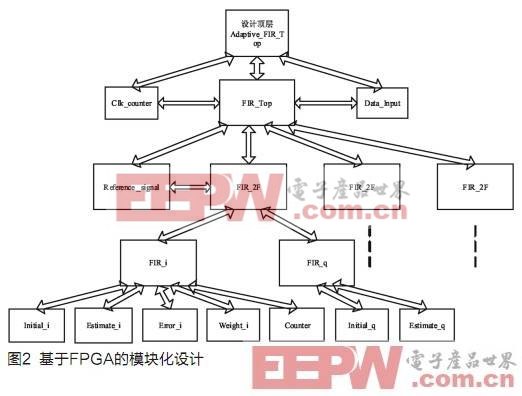

在本設(shè)計(jì)中應(yīng)該綜合考慮各方面因素,選擇一種最佳模塊結(jié)構(gòu)和模塊規(guī)模。本設(shè)計(jì)中的結(jié)構(gòu)化層次是由一個(gè)頂層模塊和若干個(gè)子模塊組成,每個(gè)子模塊根據(jù)需要再包含自己的子模塊,以此類(lèi)推,共5層,如圖2所示。

本設(shè)計(jì)中,整個(gè)通道失配校準(zhǔn)模塊共需要90個(gè)乘法器。這些乘法器如果采用FPGA的邏輯資源直接構(gòu)建,不僅難以保證理想的運(yùn)算速度,而且硬件開(kāi)銷(xiāo)非常巨大。而FPGA芯片內(nèi)部已經(jīng)集成了18×18位的硬件乘法器模塊,其速度快,實(shí)現(xiàn)簡(jiǎn)單,能有效節(jié)省FPGA的邏輯資源。由于系統(tǒng)設(shè)計(jì)時(shí)選用的FPGA芯片型號(hào)為Xilinx公司的xc2v8000ff1152-5,它集成了幾百個(gè)硬件乘法器,因此可以全部使用硬件乘法器來(lái)完成相應(yīng)的乘法運(yùn)算。

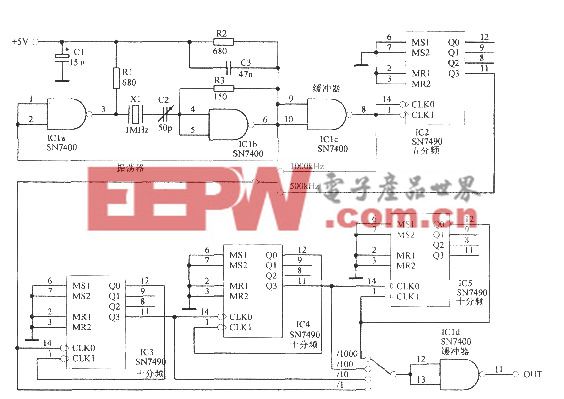

采用VHDL語(yǔ)言編寫(xiě)實(shí)現(xiàn)程序,開(kāi)發(fā)環(huán)境為ISE 8.2i,綜合工具為Synplify Pro v8.1,仿真工具為ModelSim SE 6.3f。圖3所示的是程序經(jīng)Synplify Pro v8.1綜合后得到的LMS自適應(yīng)校正濾波器頂層模塊RTL視圖。RTL視圖即寄存器傳輸級(jí)視圖,該圖高度抽象為模塊化結(jié)構(gòu),它是在對(duì)源代碼編譯后再現(xiàn)設(shè)計(jì)的寄存器傳輸級(jí)原理圖。

所有算法模塊均在全局使能信號(hào)clk_en不同狀態(tài)的控制下進(jìn)行工作,從而使算法運(yùn)行達(dá)到8M周期,直至找到最佳權(quán)值,最終完成多通道校準(zhǔn)的任務(wù),實(shí)現(xiàn)多個(gè)通道的幅相一致性。

表1為多通道校準(zhǔn)算法的FPGA資源占用列表,從系統(tǒng)資源占用情況可以看出:多通道校準(zhǔn)算法FPGA實(shí)現(xiàn)過(guò)程中,如果再加上前后端處理程序一起編譯,則輸入輸出端口將減少,資源占用也將減少,并不影響系統(tǒng)實(shí)現(xiàn)。其它各種資源占用量都較少,完全符合FPGA設(shè)計(jì)要求。

評(píng)論