基于FPGA和DSP的衛星導航接收機測試平臺

引言

衛星導航接收機是衛星導航系統的用戶終端,用以給用戶提供精確的經度、緯度、高度和速度等信息。現在,衛星導航接收機已經應用于航空,交通管理,石油等各個領域,針對衛星導航接收機的研究也越發深入。

本文介紹了一種以 FPGA和 DSP為主處理器的衛星導航接收機硬件平臺。在該平臺上不僅可以驗證針對現在所有衛星導航系統(GPS,Glonass,伽利略,北斗)的基帶信號處理算法和導航解算算法,同時也可以實現完整的單頻、雙頻或者兼容接收機。

1 硬件設計

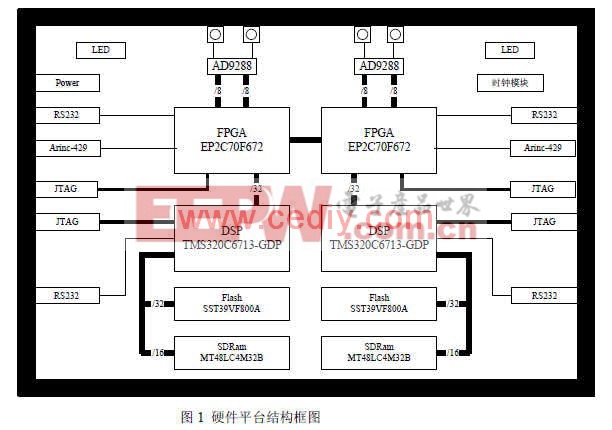

1.1 硬件平臺組成硬件平臺結構框圖如圖 1所示。

該平臺以兩片 FPGA芯片和兩片 DSP芯片為主處理器。經過 AD采樣后的信號直接進入FPGA,此后所有對信號的處理均由軟件來實現。如此可以充分利用 FPGA和 DSP的重復燒寫及在線調試能力,

盡量減少對硬件的依賴程度,從而增加平臺的靈活性。另外,每片 DSP都外接了 Flash和 SDRAM。由于 Flash掉電數據不會丟失,可以在 Flash內保存程序及數據,功能有如 PC機上的硬盤,而外接的 SDRAM是 DSP的擴展Ram,當 DSP運行大型程序(如導航解算程序)以致 DSP的內部 Ram不夠用時,可以將程序放到外接的 SDRAM內運行。

平臺上還有多個串口,可以接顯控等設備。兩個 Arinc-429接口可以接慣導等航空設備。JTAG是在線調試接口。時鐘模塊提供系統的工作時鐘。

只要連接上針對不同衛星導航系統的射頻模塊和天線,該平臺就可以成為一個完整的接收機。

1.2 芯片介紹

FPGA采用 Altera公司 CycloneII系列中的 EP2C70F672。Altera公司的 CycloneII系列 FPGA是業界成本及功耗最低的 FPGA之一,采用 90nm工藝制造。 EP2C70F672是 CycloneII系列中的最高型號,擁有 7萬個邏輯單元, 1Mbits內部 RAM,300個 9×9乘法器,4個 PLL環和 422個 I/O接口,最高數據率可以達到 330Mbps。

DSP采用德州儀器公司(TI)的C6000系列中的TMS320C6713。它是TI開發的基于甚長指令(VILW)結構浮點運算數字信號處理芯片,每周期可以執行 8條32位指令,工作頻率最高可以達到300MHz。擁有 256K字節內部RAM,16個通道的增強 DMA控制器,32bits外部存儲器接口,兩個多通道緩沖口。

模數轉換芯片選用模擬器件公司(ADI)的 AD9288Bst-100。該芯片的采樣率最高可以達到100Msps,正交雙通道 8bits輸出。由于其低功耗特性,被廣泛應用于手持設備等對功耗要求較高的場合。

Flash采用SST公司的 SST39VF800,容量為 512K*16。SDRAM采用 Micron公司的 MT48LC4M32B,存儲空間為4M*32。

2軟件測試

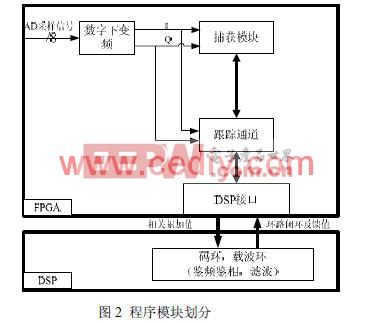

在該硬件平臺上用 Verilog語言和 C語言編寫了簡單的 GPS衛星捕獲跟蹤程序,以驗證其功能。程序模塊劃分如圖 2所示。在 FPGA內實現了數字下變頻,捕獲和跟蹤通道,在 DSP內實現跟蹤環

路的鑒頻鑒相算法以及環路濾波器。經過 A/D采樣的 8bit信號通過下變頻模塊后輸出 I/Q兩路正交基帶信號。I/Q基帶信號分別進入捕獲模塊和跟蹤通道模塊。在成功捕獲到信號后轉入跟蹤。跟蹤通道每次輸出的相關累加值經過 DSP接口模塊傳給 DSP。DSP利用接收到的相關峰值進行鑒相鑒頻和濾波,并將濾波結果反饋給 FPGA形成閉環。

評論