一種通用SPI總線接口的FPGA設計與實現

2.3 FIFO模塊由于微處理器的寫數據速率遠比串口輸出速率快得多,所以必須先將數據保存于緩沖區,FIFO的容量應根據通信數據量的大小來確定,在本設計中,由于數據量不大,所以定義了一個 64 X 8位的異步 FIFO寄存器,用于保存收發數據,用 VHDL硬件描述語言描述的FIFO是一個 64 X 8位的數組。模塊包括兩個時鐘信號,寫入和讀出數據總線,滿標志和空標志信號,當 FIFO為滿標志時,寫入的數據將被忽略。

2.4配置模塊 該模塊設計了2 個 3 X 12位的RAM,一個用于保存主機模塊配置參數,另一個用于保存從機模式配置參數,每次主從機模式切換時將配置參數發送到數據收發模塊。數據收發模塊根據配置參數調整分頻倍數、相位、輸出順序(高位先出或低位先出)、幀長度等。

2.5數據收發模塊

該模塊實現與從設備的通信。在主機模式下,將 FIFO的并行數據進行并串變換,然后通過 MOSI引腳輸出數據,并同時輸出驅動時鐘和控制信號(低電平)。在從機模式下將串行輸入的數據串并變換后寫入 FIFO模塊中。

四、仿真與驗證

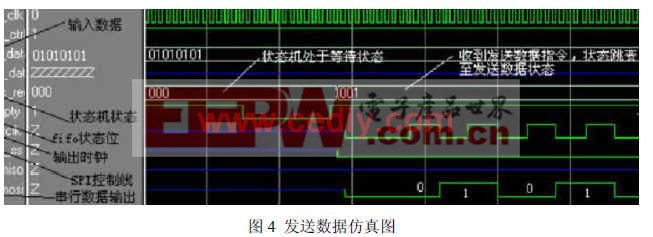

將用 vhdl描述好的 SPI接口電路用 synplify進行綜合,然后用 modelsim軟件進行仿真。先仿真微處理器通過 SPI接口發送數據過程,在地址總線上輸入指令寄存器地址,在數據總線上輸入發送數據指令,工作時鐘為89.6M,然后在地址總線上輸入寫數據寄存器地址,在數據總線上輸入數據 01010101。得到如圖 3所示的部分管腳的波形。

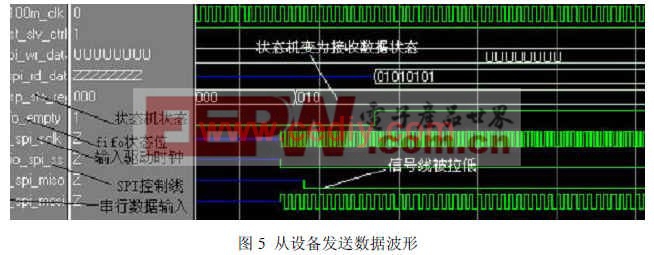

然后仿真從設備發送數據過程,首先往 SPI模塊的 ss管腳輸入低電平,同時從 sclk管腳輸入驅動時鐘,在 mosi管腳輸入數據,得到圖 4所示的波形。

用 quartus軟件進行編譯后,將生成的網表文件通過 JTAG下載到 altera公司的 acex1k系列 EP1k30TC144-3運行,配合設計好的單片機程序,分別給 FPGA輸入 44.8M和 89.6M工作時鐘,在 quartus的 signal tap的輔助分析下都得到了正確的結果。 EP1k30TC144-3芯片共有1728個邏輯單元,本設計使用了 138個,占系統資源的7%,是個比較理想的結果。

五、結束語隨著半導體技術的進步,FPGA的價格越來越便宜,工作頻率越來越高,使用 FPGA實現 SPI通信接口是切實可行的,本文作者創新點: 1、將總線控制信號封裝成指令,使用者只需通過發送指令的方式操作,避免了復雜的

時序邏輯設計問題。 2、可以在 SPI工作過程中隨時調整配置參數。 3、充分考慮了可測試性設計,使用者可隨時查看 SPI總線工作狀態。

評論