一種通用SPI總線接口的FPGA設計與實現

2、模塊設計

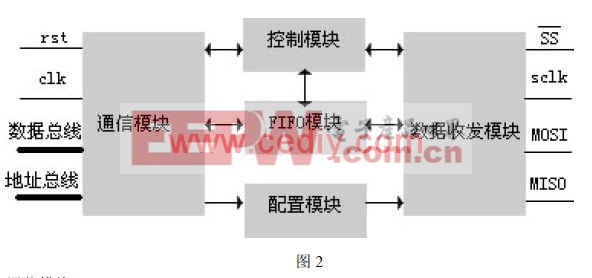

根據 SPI總線的原理,可分為以下功能模塊:通信模塊,控制模塊,FIFO模塊(緩沖存儲器),配置模塊,數據收發模塊,如圖 2所示。

2.1通信模塊

這個模塊實現與微處理器的通信,接收微處理器的數據和指令,通過指令解析,發出控制信號。該模塊定義的寄存器包括發送數據寄存器,接收數據寄存器,測試數據寄存器,接收測試數據寄存器,指令寄存器,配置寄存器,狀態寄存器,各寄存器詳述如下:

發送數據寄存器:可寫寄存器,接收微處理器發送的數據,而后暫存于 FIFO模塊中;

接收數據寄存器:可讀寄存器,當收到讀數據指令時,該寄存器將從 FIFO中讀入數據且通過數據總線發送至微處理器;

測試數據寄存器:可寫寄存器,用于在測試模式下接收測試數據,而后暫存于 FIFO模塊中;

接收測試數據寄存器:可讀寄存器,當收到讀測試數據指令時,該寄存器讀入 FIFO中的測試數據,并通過數據總線發送至微處理器,以測試各功能模塊工作是否正常;

指令寄存器:可寫寄存器,接收微處理器的指令,通過指令解析后,往其它模塊發出相應的控制信號,包括發送數據指令,讀數據指令,復位指令,寫測試數據指令,讀測試數據指令;

配置寄存器:可寫寄存器,用于保存 SPI配置參數,包括時鐘分頻倍數、相位、移位順序、幀長度等。該寄存器的值將被轉發至配置模塊。

狀態寄存器:只讀寄存器,控制模塊將狀態機狀態寫入該寄存器,供微處理器查詢 SPI

工作狀態;

2.2控制模塊

控制模塊是本系統的核心,控制著整個工作流程,為了方便結構化設計,本模塊設計了狀態機。根據 SPI總線的原理可將總線分為五種狀態,分別是等待狀態、數據發送狀態、數據接收狀態、數據接收完畢狀態、在線測試狀態。各狀態之間的關系如圖 2所示:

評論