基于FPGA的兩路視頻同步播放系統(tǒng)的設(shè)計(jì)

2.1 硬件系統(tǒng)總體設(shè)計(jì)

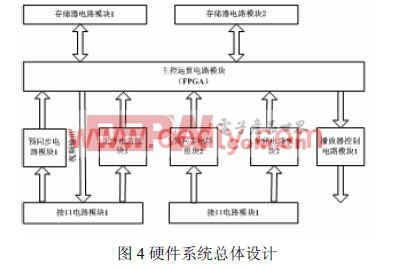

如圖 3.1所示,兩路視頻同步播放系統(tǒng)由接口電路、輸入視頻信號(hào)預(yù)同步電路、輸入視頻信號(hào)重疊區(qū)域圖像采樣窗電路、數(shù)據(jù)存儲(chǔ)電路、主控運(yùn)算及播放器控制電路組成。

本文引用地址:http://www.104case.com/article/191936.htm

本文引用地址:http://www.104case.com/article/191936.htm2.2 主要硬件功能模塊電路設(shè)計(jì)與測(cè)試

2.2.1 接口電路模塊設(shè)計(jì)

接口1和接口2分別將兩路視頻信號(hào)由播放器引入后續(xù)處理模塊,并將處理后的視頻信號(hào)輸出給顯示系統(tǒng)。

2.2.2 預(yù)同步電路模塊設(shè)計(jì)兩路輸入視頻信號(hào)在進(jìn)行同步處理前需要首先進(jìn)行緩沖,以期在同一時(shí)刻到達(dá)主控模塊上一致。本系統(tǒng)采用兩片有 FPGA芯片控制的 FIFO芯片分別實(shí)現(xiàn)兩路信號(hào)的預(yù)同步功能。

本系統(tǒng)采用uPD42280芯片。 uPD42280是容量為256kbyte*8bit (262, 224 * 8bit)的高速場(chǎng)存儲(chǔ)器。CMOS動(dòng)態(tài)電路實(shí)現(xiàn)了芯片的高速和低功耗。 uPD42280O可以設(shè)置為同步或異步讀寫(xiě)的FIFO。其中, DI0-7為數(shù)據(jù)輸入,DO0-7為數(shù)據(jù)輸出;/WE、/RE分別為寫(xiě)使能和讀使能; /WRST、/RRST分別為寫(xiě)復(fù)位和讀復(fù)位; VDD、GND分別為電源和接地。而在進(jìn)行預(yù)同步處理時(shí),兩路輸入的視頻信號(hào)均為隔行PAL制黑白信號(hào),其中亮度信號(hào)為8位,即每幀圖像大小為702*288*8/1024/8=198Kbyte,所以 uPD42280的容量足夠一場(chǎng)圖像的存儲(chǔ)。

評(píng)論