基于CPCI總線的通用FPGA信號處理板的設(shè)計

輸入時寬帶寬積為1 028的線性調(diào)頻信號,系統(tǒng)實測脈壓實部虛部以及模值,如圖9所示。本文引用地址:http://www.104case.com/article/191878.htm

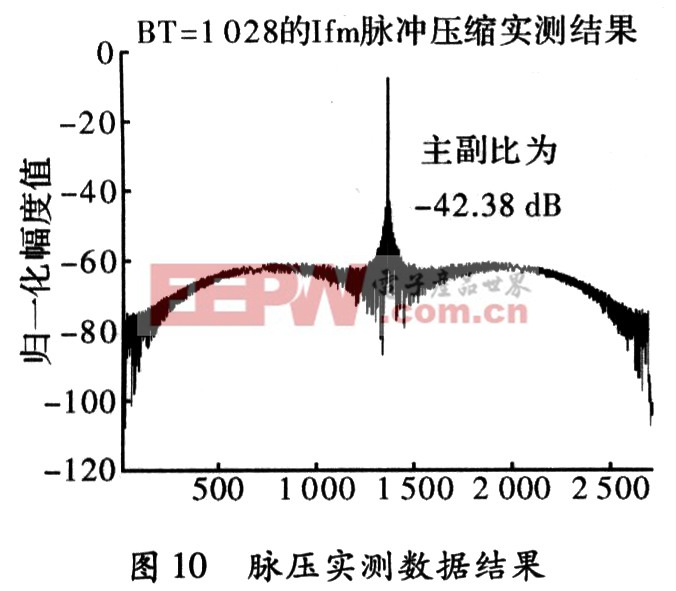

把實測數(shù)據(jù)導(dǎo)人Matlab進行分析,得到主副比為-42.38 dB,滿足了系統(tǒng)的要求,如圖10所示。

通用信號處理板實物圖,如圖11所示。

3 結(jié)束語

文中設(shè)計的基于CPCI總線的通用FPGA信號處理板,具有龐大的數(shù)據(jù)處理能力和高實時性,在實際應(yīng)用中實現(xiàn)了數(shù)字下變頻,大時寬帶寬積數(shù)字脈沖壓縮等功能。不用過多考慮硬件設(shè)計問題,只要根據(jù)通用信號處理板上的資源情況,將設(shè)計任務(wù)合理地配置到板上各處理單元中,就可提高系統(tǒng)的可靠性,縮短設(shè)計周期。這對于數(shù)據(jù)處理要求高、實時性強、數(shù)據(jù)量大、處理算法復(fù)雜多變的雷達信號處理系統(tǒng),有著重要的實際意義。

評論