在FPGA上對OC8051IP核的修改與測試

(4)oc8051_decoder模塊

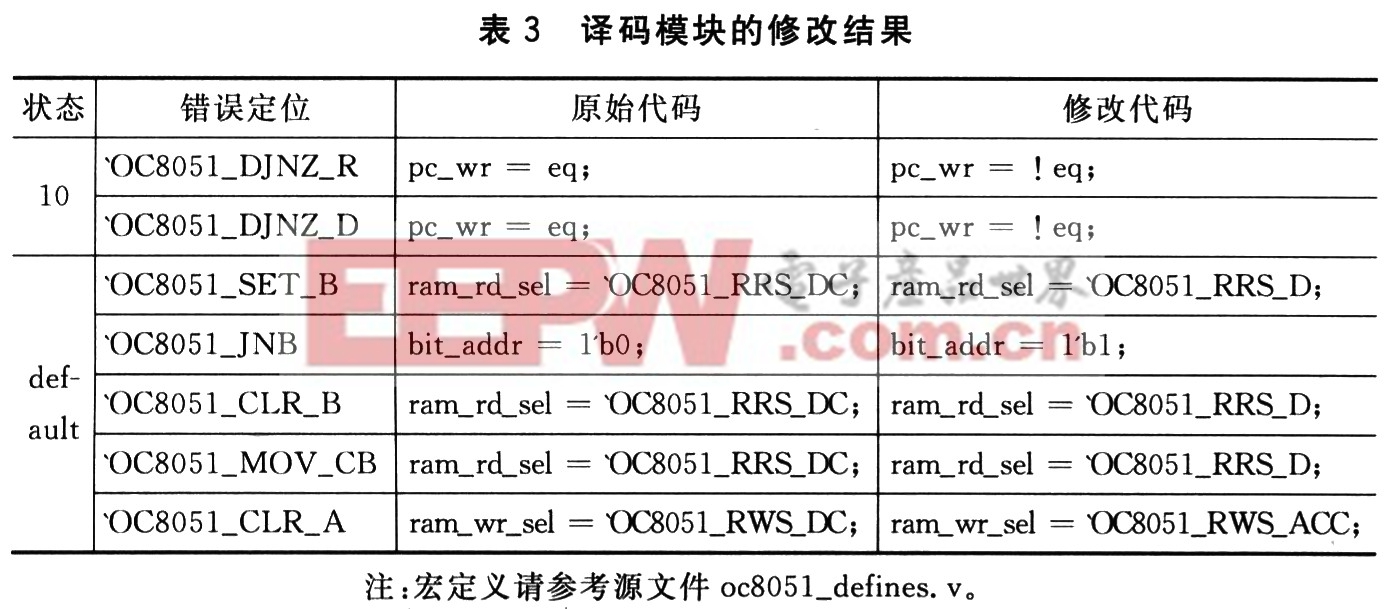

該模塊用于對指令譯碼。其設(shè)計思想是,分析當前輸入信號op_in和所處狀態(tài)state,把指令的功能配置為其他模塊的控制信號,并得出下一個狀態(tài)。因為各指令的指令周期不同,所以每條指令譯碼執(zhí)行狀態(tài)也各有不同。模塊主體由狀態(tài)機構(gòu)成,在每個狀態(tài)下對狀態(tài)機不同的執(zhí)行狀態(tài)進行條件判斷嵌套,以此實現(xiàn)對不同指令的多路選擇。對模塊仿真時發(fā)現(xiàn),執(zhí)行如DJNZ、JB、CLR等指令的結(jié)果不正確,其原因是在某些狀態(tài)下對某些指令的譯碼有誤,主要表現(xiàn)為配置了錯誤的控制信號。對模塊修改結(jié)果如表3所列。本文引用地址:http://www.104case.com/article/191853.htm

2.3 仿真結(jié)果

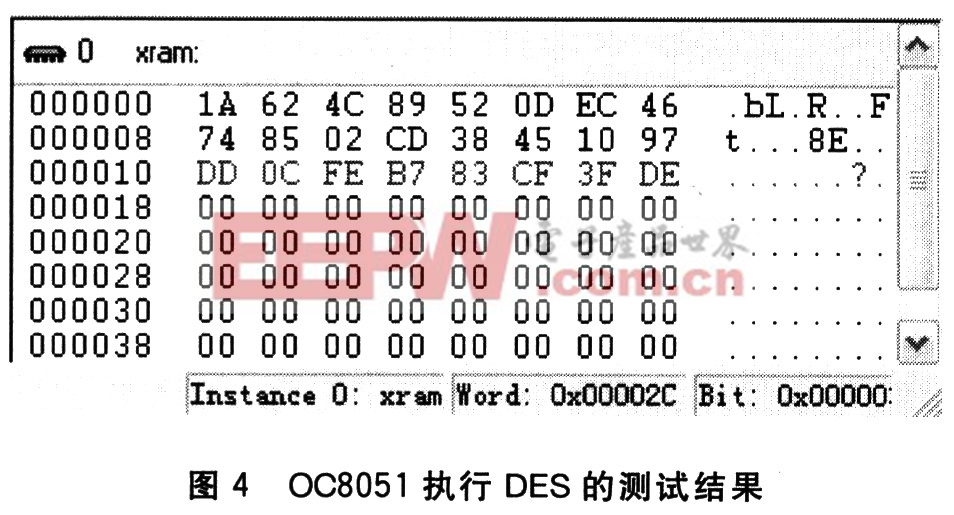

程序執(zhí)行方式是單片機的基本工作方式,通常可以分為單步執(zhí)行和連續(xù)執(zhí)行兩種。事實上,2.2小節(jié)中的具體修改方法正是結(jié)合這兩種工作方式實現(xiàn)的。數(shù)據(jù)加密標準(DES)是著名的對稱密鑰分組密碼,由美國標準FIPS 46-2定義。基于8051指令系統(tǒng),DES的軟件實現(xiàn)難度不大,但它是對OC8051 IP核工作能力的一次綜合檢驗。采用DEs標準測試向量:

密鑰K=1A624C89520DEC46

明文P=748502CD38451097

密文C=DD0CFEB783CF3FDE

結(jié)合圖2所示的仿真調(diào)試方案,Modelsim環(huán)境中OC8051執(zhí)行DES的仿真結(jié)果如圖3所示。

3 基于FPGA的下載測試

利用FPGA對其功能進行了驗證。選用Altera公司的EP2C35F672C6型號FPGA開發(fā)板,含有33 216個邏輯單元(LE)、豐富的存儲器(RAM)和4個鎖相環(huán)(PLL)。采用QuartusII軟件,OC8051 IP核綜合后占用3 917個邏輯單元,時鐘頻率最高達到30.81 MHz,F(xiàn)PGA測試的實際頻率為27 MHz。

利用QuartusII對OC8051 IP核綜合、布局布線后,采用JTAG方式將配置文件下載至FPGA中,測試程序仍采用DES算法程序。In-System Memory ContentEditor是QuartusII提供的一個可在線操作FPGA片上RAM內(nèi)容的工具,通過JTAG方式,用戶可以查看和修改RAM中的內(nèi)容。如果用戶設(shè)計對RAM中的內(nèi)容進行了修改,需要查看修改后的結(jié)果是否為所期望的,則使用該工具最為方便。OC8051 IP核外部RAM中的數(shù)據(jù)可以通過該工具方便地操作,所以本文對DES測試向量的輸入和輸出都是通過它來完成的,如圖4所示。

FPGA下載測試結(jié)果表明,OC8051工作正常,與仿真結(jié)果一樣,測試程序運行正確。

結(jié) 語

本文介紹了一種OC8051 IP核的仿真測試方案。該方案給出了查找與定位IP核中邏輯錯誤的方法,并詳細介紹了各種錯誤的修改方法。測試結(jié)果表明,OC8051工作正常,已經(jīng)初步具備了微控制器的功能,可以被運用于實際的工程開發(fā)中。

評論