在FPGA上對OC8051IP核的修改與測試

引 言

20世紀80年代初,Intel公司推出了MCS-51單片機,隨后Intel以專利轉讓的形式把8051內核發布給許多半導體廠家,從而出現了許多與MCS-51系統兼容的產品。這些產品與MCS-51的系統結構相同,采用CMOS工藝,因而常用80C51系列來指代所有具有8051指令系統的單片機。在80C51系列中,OC8051以架構清晰、取指帶寬大、時鐘效率高等諸多優點受到業內人士的青睞。本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

1 OC8051結構分析

OpenCores網站提供的OC8051 IP核與8051的系統結構相同,如圖1所示。該IP核兼容所有8051指令系統,內部資源包括:8位CPU,尋址能力達2×64K;4 KB的ROM和128字節的RAM;4個8位I/O口;16位內部定時/計數器;5個中斷源和2個中斷優先級。采用Verilog語言對其各個模塊進行描述。系統主要模塊及其功能說明如表1所列。不同模塊對應的源文件均是以模塊名稱命名的,例如累加器A對應的源文件為oc8051_acc.v。

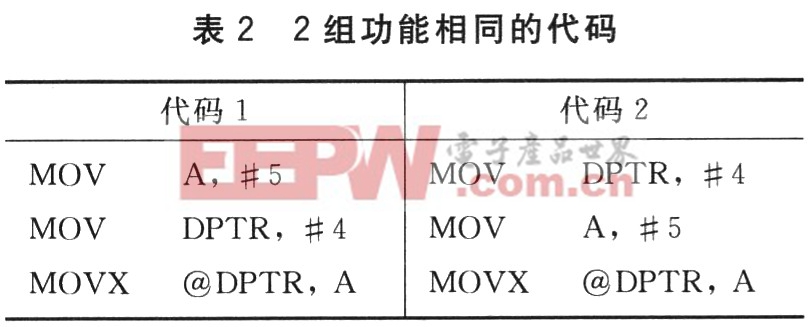

雖然上述OC8051 IP核宣稱兼容所有8051指令系統,但是實際執行時并非如此。例如在執行表2所列的2組功能相同的代碼時,所得到的執行結果并不相同。代碼1的執行結果是將5寫入地址為0的外部RAM,代碼2的執行結果是將5寫入地址為4的外部RAM。造成這種現象的原因是,oc8051_ext_addr_sel模塊配置寫外部RAM地址時延誤了一個時鐘周期。若要OC8051 IP核與標準8051系統一致,須對源文件中類似的邏輯錯誤進行修改。

|

|

2 OC805 1仿真調試及修改

對于硬件設計而言,仿真的作用是驗證設計結果的邏輯功能是否符合初始規定,如果在這一層次上設計出了問題,那么以后各個層次的工作將完全不確定。由前文可知,OC8051 IP核存在著邏輯錯誤,所以有必要通過仿真的手段實現錯誤查找和定位,從而最終完成對邏輯錯誤的修改。

評論