基于FPGA的提取位同步時鐘DPLL設計

異或鑒相器的輸出為:

q(n)=q(n-1)+p(n) (2)

由上可得出反饋信號周期與輸入信號周期的差分方程:

to(n)=ts(n-1)+q(n-1)+ε{u(n-1)?[ts(n-1)-ts(n-2)]} (3)

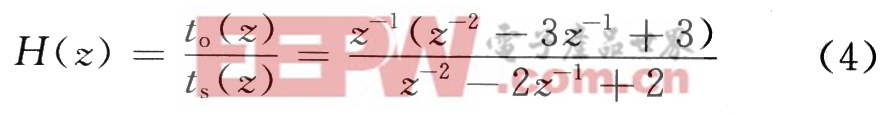

式中:ε[?]是由于相位差引入的一個二階量,當p(n)很小時,ε[?]是一個無窮小的量。在p(0)=O,q(O)==0,ε[?]=0的情況下,對式(3)進行z變換得:

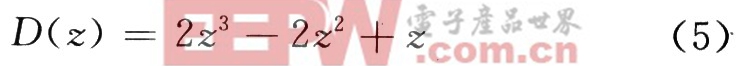

其特征方程為:

解得:

z1,2=0.5±0.5i,z3=0

由于|z1,2|=0.7071,|z3|=0

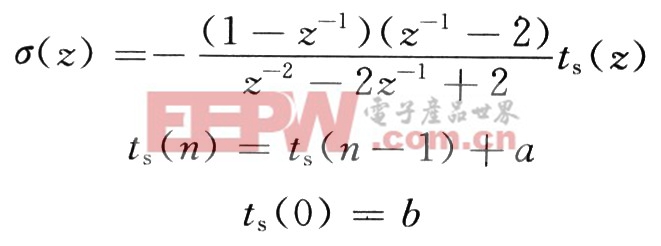

由此可知,系統穩定。接下來討論系統對輸入信號的跟蹤誤差:

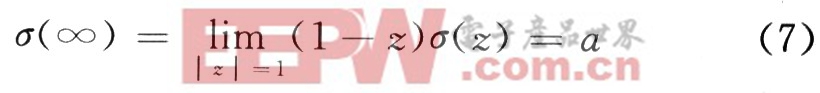

式中:b>0,當|b|/|a|足夠小時,對上式做單邊z變換,利用中值定理得:

由此可見,穩態誤差取決于輸入信號與本地信號初始相位誤差。由于系統最后穩定在120 ns內,而每個待鎖定碼元的寬度是2 000 ns,使用△表示鎖定后的最大誤差范圍,可得:

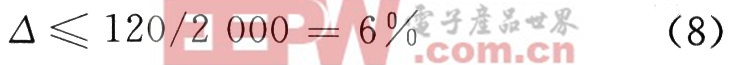

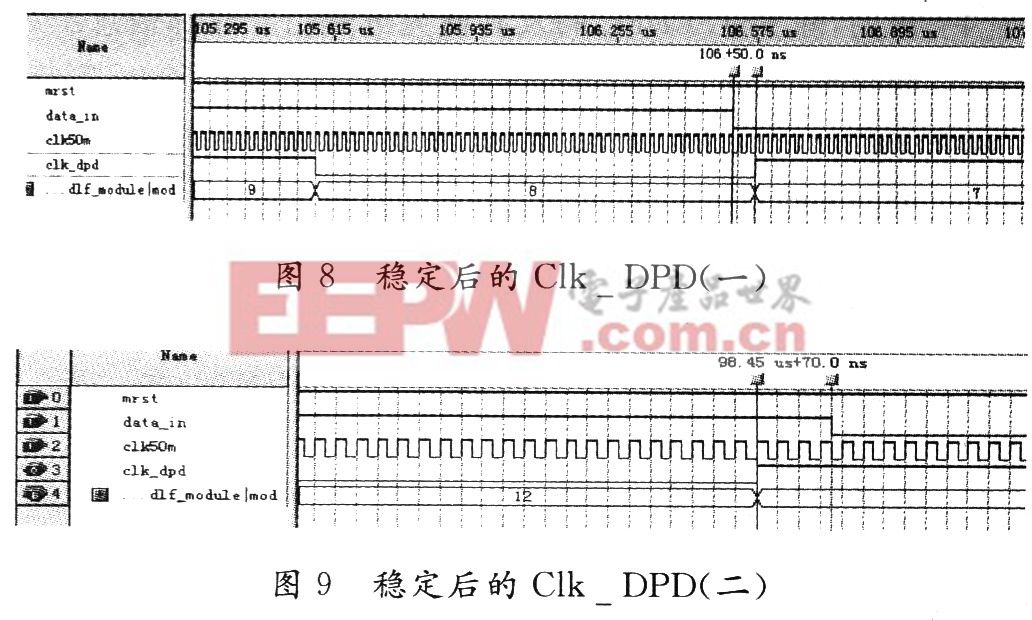

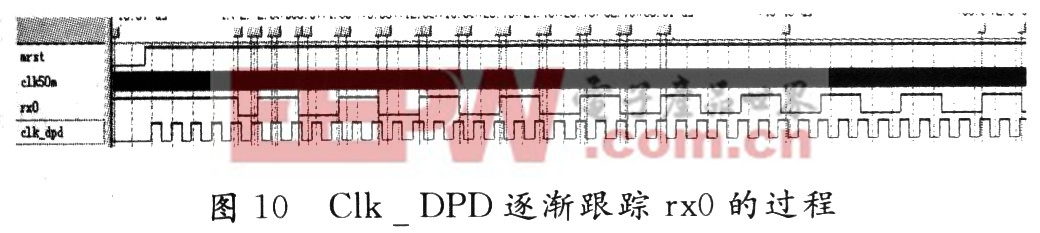

可見,穩定后,偏移量△最多不超過6%。所以120 ns的穩態誤差能滿足需要,系統可根據DPLL輸出周期為2μs的同步位時鐘下降沿可靠采樣,避免了亞穩態現象的發生。穩定后的Clk_DPD如圖8、圖9所示,滯后50ns,累計4次后,超前70ns,穩定于絕對誤差120ns。Clk_DPD逐漸跟蹤rx0提取出其中隱含的位時鐘的過程如圖10所示。

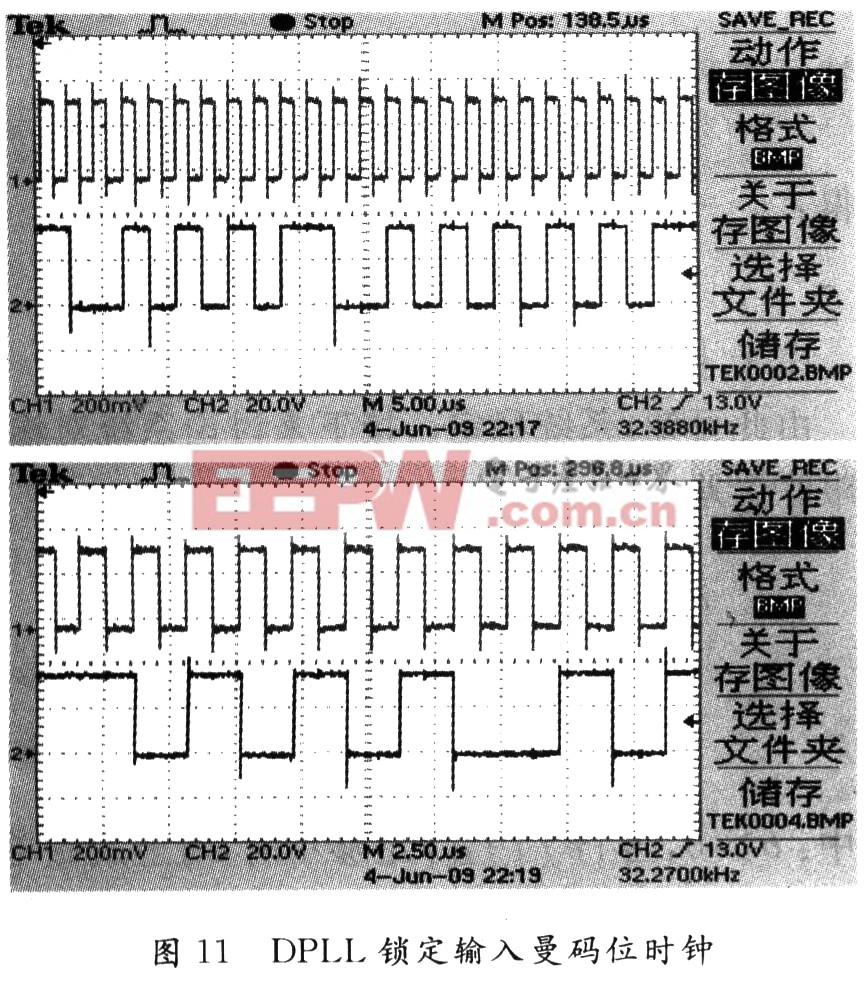

示波器撲捉到DPLL鎖定輸入的曼徹斯特碼位時鐘的波形如圖11所示。

4 結 語

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數字鎖相環設計方法。應用Verilog硬件描述語言使設計更加靈活,不僅縮短了設計周期,而且可實現復雜的數字電路系統。本文測試中所用的待鎖定輸人數據由AM7960芯片輸出的曼徹斯特碼提供,通信速率為250 Kb/s,經由MAx3485轉換成LVTTL電平信號,輸入FPGA芯片EPlC3T10017。由于曼徹斯特碼在每個碼元內有一次跳變,鎖定后的時鐘是500 Kb/s。經仿真測試,該DPLL具有鎖定相位時間短,鎖定后相位穩定的特點,最大偏差不超過6%,這在理論上已加以證明,從而驗證了設汁的正確性。

數字通信相關文章:數字通信原理

鑒相器相關文章:鑒相器原理

評論