基于FPGA的提取位同步時鐘DPLL設計

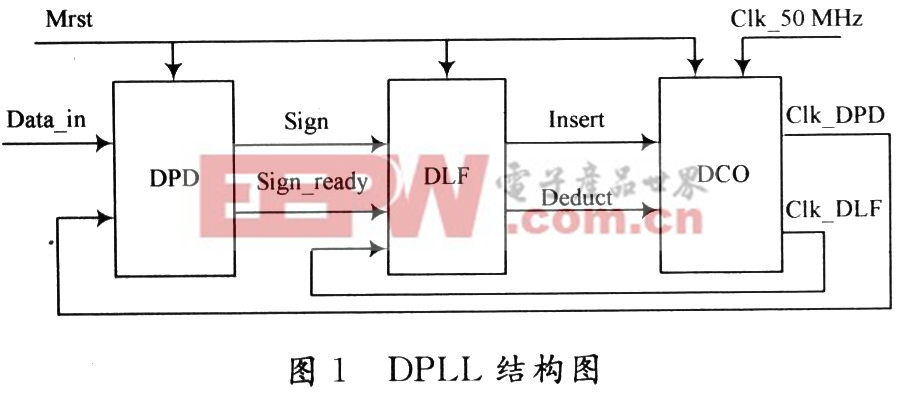

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發同步,而且在獲取幀同步及對接收的數字碼元進行各種處理的過程中也為系統提供了一個基準的同步時鐘。位同步的目的是使每個碼元得到最佳的解調和判決。位同步可以分為外同步法和自同步法兩大類。一般而言,自同步法應用較多。外同步法需要另外專門傳輸位同步信息。自同步法則是從信號碼元中提取其包含的位同步信息。自同步法又可以分為兩種,即開環同步法和閉環同步法。開環法采用對輸入碼元做某種變換的方法提取位同步信息。閉環法則用比較本地時鐘和輸入信號的方法,將本地時鐘鎖定在輸入信號上。閉環法更為準確,但是也更為復雜。本文采用了自同步法,在FPGA構造片內對超前一滯后全數字鎖相環提取曼徹斯特碼中包含的位同步時鐘。1提取位同步時鐘全數字鎖相環總體結構與工作原理這種超前一滯后全數字鎖相環采用加減門結構,每輸入一個碼元后,根據鑒相器判斷是超前還是滯后,通過反饋回路控制的加減門來調整相位,使之逼近輸入碼元的相位。一旦失步,就需要通過反饋回路重新調整。每一個超前和滯后脈沖僅能調整一步,如果接收碼元出現連“1”或是連“O”的情況,鎖定時間會很長,使其同步建立時間和調整精度變得相互制約。盡管有此缺點,但由于這種結構具有失鎖后的自我調節性,因此,碼元消失或是碼元相位出現抖動時,同步脈沖不會出現較大變化,仍然可以輸出穩定的同步脈沖。由于采用曼徹斯特碼進行傳輸,該設計主要應用于地鐵車輛總線上,傳輸速率為250 Kb/s,速率較低,且每個碼元內都有一次電平跳變,不會出現連續的“O”或“1”,因此采用閉環的超前一滯后全數字鎖相環非常適合提取比特流中的位時鐘。基本結構如圖1所示,主要由數字鑒相器(DPD)、數字環路濾波器(DLF)、數控振蕩器(DCO)三部分構成。DPLL是一種相位反饋控制系統,它將輸入信號Data_in與本地恢復時鐘Clk_DPD之間的相位誤差(超前還是滯后)信號送入數字環路濾波器DLF中,對相位誤差信號進行平滑濾波,并生成控制DCO動作的控制信號,DCO根據控制信號給出的指令,調節內部高速振蕩器的震蕩頻率,通過連續不斷的反饋調節,使其輸出時鐘Clk_DPD的相位跟蹤輸入數據Data_in的相位。

2 環路功能及其實現方法

下面沿環路依次介紹DPLL環路各個組成模塊的詳細功能、內部結構、對外接口信號及實現方法。

2.1 鑒相器結構及其工作原理

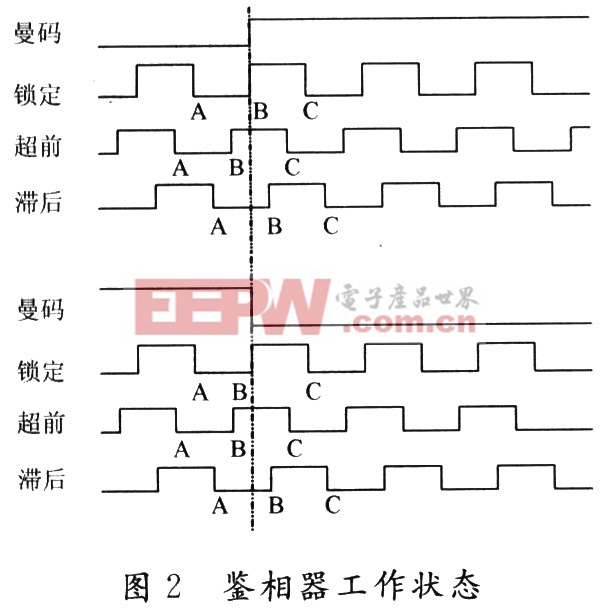

超前一滯后型數字鑒相器輸出一個表示本地估算信號超前或滯后于輸入信號的量。如果本地估算信號超前于輸入信號,則輸出“超前脈沖”,以便利用該“超前脈沖”控制本地估算信號的相位推后。反之,則輸出“滯后脈沖”,并使本地估算信號的相位前移,這樣隱含在曼徹斯特碼中的位時鐘就被鑒相器比較了出來。超前一滯后型數字鑒相器可分為積分型和微分型兩種。積分型超前一滯后數字鑒相器,結構和硬件實現比較復雜,但具有優良的抗干擾性能。而微分型數字鑒相器結構相對簡潔,硬件實現也比較簡單,但是它的抗干擾能力比較差。這里采用微分型超前一滯后型數字鑒相器,將抗干擾的任務留給后面的數字濾波器環節實現。DPD的工作狀態如圖2所示。

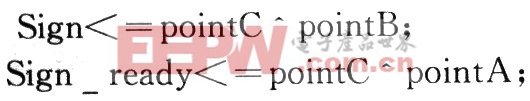

當Sign為1時,表示本地時鐘超前于輸入信號;當Sign為O時,表示本地時鐘落后于輸入信號。

當Sign_ready=1時,表示輸入信號有跳變,Sign有效;當Sign_readyr=0時,表示輸入信號無跳變,Sign無效。

微分型超前一滯后數字鑒相器的原理圖如圖3所示。

2.2 數字濾波器結構及其買現方法

在數字鎖相環路中,環路濾波器通常使用數字濾波器,它們與模擬鎖相環路中的模擬環路濾波器相對應。數字環路濾波器在環路中對輸入噪聲起抑制作用,并且對環路的校正速度起調節作用。

數字通信相關文章:數字通信原理

鑒相器相關文章:鑒相器原理

評論