采用帶有收發(fā)器的全系列40-nm FPGA 和ASIC 實現(xiàn)創(chuàng)

工藝技術(shù)和40-nm 的優(yōu)勢和以前的65-nm 節(jié)點以及最近的45-nm 節(jié)點相比, 40-nm 工藝有很大的優(yōu)勢。最顯著的一點是更高的集成度,半導(dǎo)體生產(chǎn)商可以在更小的管芯中集成更多的功能,生產(chǎn)出密度更高的器件。

40-nm 工藝還進(jìn)一步提高了性能。40 nm 最小的晶體管邏輯門長度比65 nm 邏輯門長度短38.5%,比45-nm 工藝的邏輯門長度短11%。40 nm 的阻抗進(jìn)一步降低,從而提高了驅(qū)動能力,實現(xiàn)了性能更好的晶體管。應(yīng)變硅技術(shù)使電子和空穴的移動能力提高了30%,晶體管性能提高了近40%。

采用帶有收發(fā)器的全系列40-nm FPGA 和ASIC 實現(xiàn)創(chuàng)新設(shè)計Altera 公司

4

雖然密度和性能的提高非常顯著,但是,當(dāng)今系統(tǒng)開發(fā)人員在設(shè)計中需要著重考慮的是功耗問題。40-nm節(jié)點在功耗上也有一定的優(yōu)勢,更小的工藝尺寸減小了導(dǎo)致動態(tài)功耗的雜散電容。特別是,臺積電(TSMC)的40-nm 工藝技術(shù)要比其45-nm 工藝技術(shù)的有功功耗低15%。(2)

但是,工藝尺寸的降低卻增大了待機(jī)功耗。Altera 使用多種方法來降低靜態(tài)功耗,包括多閾值晶體管、長度不同的晶體管溝道、三重氧化等,并且在對性能要求不高的PLD 上綜合考慮性能和功耗,例如配置邏輯等。

可編程功耗技術(shù)和性能

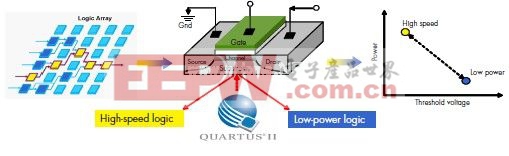

除了常用的電路設(shè)計方法, Altera 還引入了65-nm Stratix® III FPGA 的可編程功耗技術(shù)(3) 來降低靜態(tài)功耗。可編程功耗技術(shù)使靜態(tài)功耗降低了70%,在設(shè)計中以最低的功耗實現(xiàn)最好的性能。這一創(chuàng)新技術(shù)利用了這一事實――在典型設(shè)計中,全部邏輯中只有很少一部分用在關(guān)鍵時序通道上。基準(zhǔn)測試表明,時序余度很小的高性能邏輯和時序余度較大的慢速邏輯比平均為30:70。

在任何設(shè)計中, Altera 的Quartus® II 開發(fā)軟件自動確定設(shè)計中每一通道的松弛余度。這樣,通過調(diào)整晶體管的反向偏置電壓,將每一邏輯模塊、存儲器和DSP 模塊的晶體管自動設(shè)置為合適的模式――高性能或者低功耗:

■ 在低功耗模式中, Quartus II 軟件減小反向偏置電壓,使晶體管很難接通。這樣,減小了時序不重要電路中的亞閾值泄漏電流,以及無用的靜態(tài)功耗( 圖2 中的藍(lán)色部分)。

■ 在高性能模式中, Quartus II 軟件增大反向偏置電壓,時序關(guān)鍵通路上的晶體管更容易接通,以滿足設(shè)計中規(guī)定的時序約束要求,實現(xiàn)最佳性能( 圖2 中的黃色部分)。

圖2. Quartus II 軟件降低了功耗,提高了性能本文引用地址:http://www.104case.com/article/191798.htm

邏輯架構(gòu)和通用I/O

Altera 的40-nm 器件架構(gòu)使用了包括自適應(yīng)邏輯模塊(ALM)、TriMatrix 片內(nèi)存儲器模塊和DSP模塊的通用內(nèi)核邏輯體系結(jié)構(gòu)。ALM 含有一個可配置8 輸入分段式查找表(LUT)、兩個嵌入式加法器和兩個寄存器,并采用了MultiTrack 互聯(lián)結(jié)構(gòu)進(jìn)行布線,以支持高速邏輯、算法和寄存器功能,器件利用率非常高。

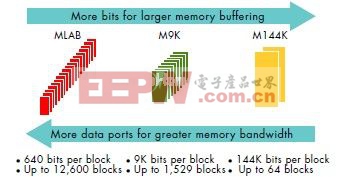

TriMatrix 片內(nèi)存儲器提供三種不同的存儲器模塊容量,大大提高了效率和靈活性,如圖3 所示。

Power

High speed

Low power

Threshold voltage

Source

Substrate

Drain

Channel

Gnd

Gate

High Speed Logic Low Power Logic

High-speed logic Low-power logic

Altera 公司 采用帶有收發(fā)器的全系列40-nm FPGA 和ASIC 實現(xiàn)創(chuàng)新設(shè)計

5

圖3. TriMatrix 存儲器結(jié)構(gòu)

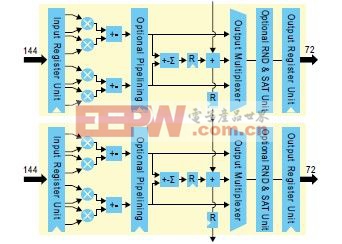

圖4 中的DSP 模塊是高性能芯片體系結(jié)構(gòu),其強(qiáng)大的可編程能力可以在多種應(yīng)用中實現(xiàn)最佳處理功能。每一模塊含有8 個18x18 乘法器,以及寄存器、加法器、減法器、累加器和求和單元,這些都是典型DSP 算法中常用的功能。DSP 模塊支持可變位寬和各種取整飽和模式,有效地滿足了應(yīng)用需求。

圖4. DSP 模塊體系結(jié)構(gòu)

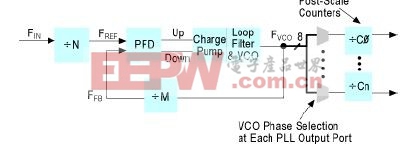

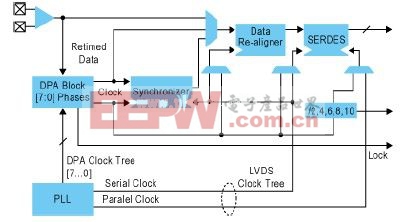

通用PLLAltera 的通用鎖相環(huán)(PLL) 包括閉環(huán)頻率控制系統(tǒng),該系統(tǒng)基于輸入時鐘信號和受控振蕩器反饋時鐘信號之間的相位差。圖5 顯示了PLL 中主要組件的簡要結(jié)構(gòu)。

6

圖5. PLL 結(jié)構(gòu)圖

這些PLL 的模擬特性使其具有非常低的抖動,能夠?qū)崿F(xiàn)可靠的時鐘方案。很多可配置時鐘輸出能夠非常靈活的實現(xiàn)系統(tǒng)時鐘,為存儲器接口和I/O 接口輸出時鐘。

最佳通用I/O 和外部存儲器接口

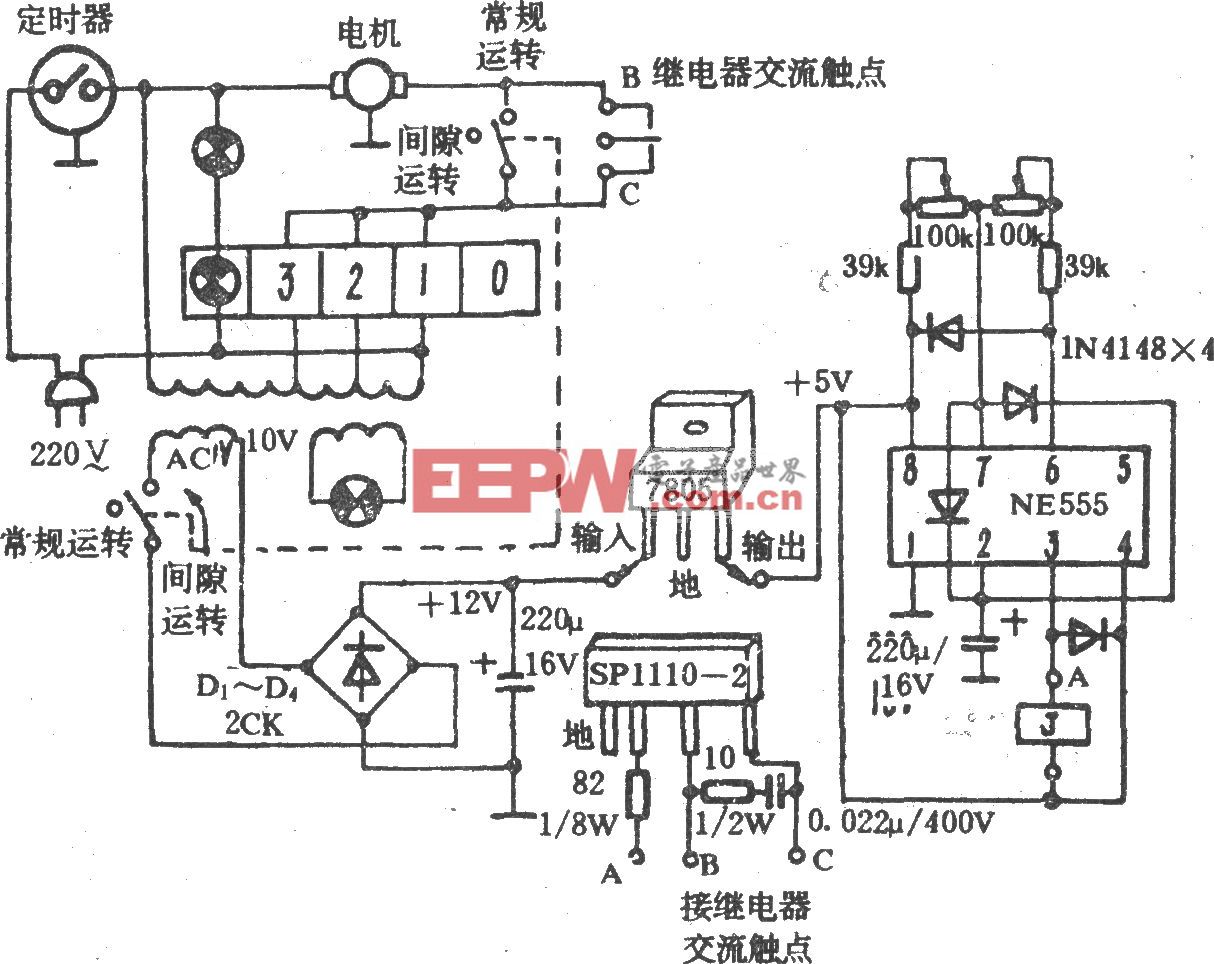

如圖6 所示, I/O 結(jié)構(gòu)的關(guān)鍵構(gòu)建模塊包括:

■ 單端I/O 支持,提供可編程擺率和驅(qū)動能力,可變延遲鏈補償電路板走線,以及串行和并行動態(tài)片內(nèi)匹

配(OCT)。

■ 支持差分片內(nèi)匹配的高性能LVDS 傳輸和接收差分信號

■ 為多通道LVDS 接口提供的硬核動態(tài)相位對齊(DPA) 模塊,避免了時鐘至通道和通道至通道偏移,以及

時鐘轉(zhuǎn)發(fā)功能,實現(xiàn)軟核時鐘數(shù)據(jù)恢復(fù)(CDR)。

圖6. DPA 結(jié)構(gòu)圖

Altera 的I/O 引腳支持已有以及新興的外部存儲器標(biāo)準(zhǔn),例如,DDR、DDR2、DDR3、QDRII、QDRII+ 和RLDRAMII 等。它們包括自校準(zhǔn)數(shù)據(jù)通路,對自己不斷進(jìn)行動態(tài)調(diào)整,在工藝、電壓和溫度變化時,提供最可靠的工作頻率。其他電路包括對齊和同步、通道去偏移、讀/ 寫調(diào)平,以及時鐘域交叉功能等。

評論