基于FPGA的超聲波氣體流量計中AGC的實現

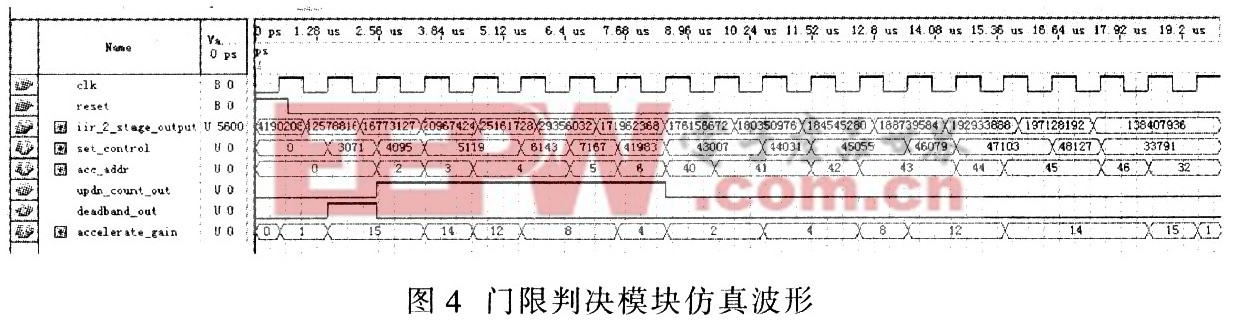

圖4是門限判決模塊的仿真波形。其中,clk為時鐘信號,reset為復位信號,iir_2_stage_output為濾波器的輸出信號,set_control為與門限進行比較的信號,acc_addr為查找表地址,updn_count_out為控制加/減計數器的計數方向,dead_band_out為控制加/減計數器的計數控制信號,accelerate_gain為控制加/減計數器的計數步進量。 本文引用地址:http://www.104case.com/article/191773.htm

從圖4中可以看出,當信號小于低門限7500時,dead_band_out=‘0’,updn_count_out=‘1’,控制加/減計數器向上計數,set_control遠離低門限,計數步進量增大;當信號大于高門限10 500時,deadband_out=‘0’,updn_count_out=‘0’,控制加/減計數器向下計數,set_control遠離高門限,計數步進量增大。

3.2.2 加/減計數器模塊

加/減計數器模塊根據輸入信號與最佳的接收信號之間的差值,對輸入信號進行反向補償。假設輸入信號經過一定衰減,AGC環路經過比較可確定接收信號電平低于最佳電平。這個差值將導致計數器向上計數,增加環路增益,直到環路濾波器的輸出重新回到門限判決模塊的兩個門限之間。如果信號乘以增益后、環路濾波器的輸出信號大于門限判決模塊的高門限時,計數器向下計數,降低環路增益,直到信號重新回到可以準確解調所需的接收信號范圍。

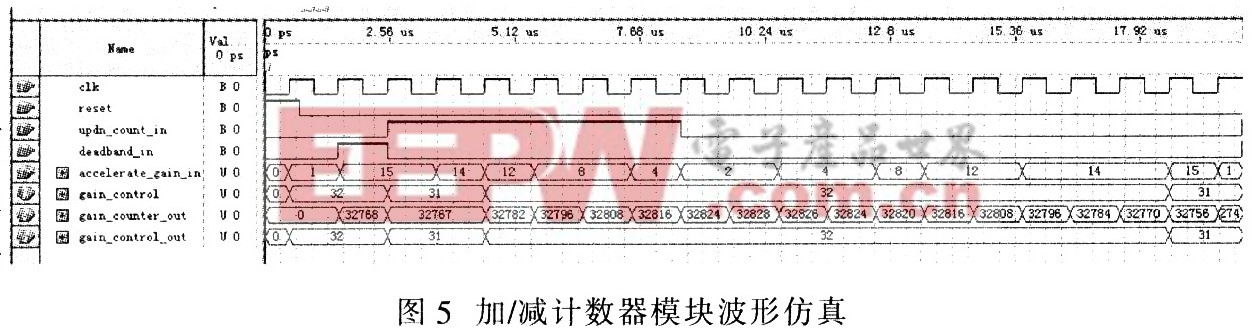

圖5是加/減計數器模塊的仿真波形。gain_counter_out為截位前的增益值,gain_control_out為截位后實際輸出的增益值。從圖5看出,當reset=‘1’時,計數器復位,設增益初始值gain_control_out=‘32’。而當deadband_in=‘O’,updn_count_in=‘1’,加/減計數器按步進量accelerate_gain_in向上計數;而當deadband_in=‘O’,updn_count_in=‘0’,加/減計數器按步進量accelerate_gainjn向下計數。計數所得的值即為輸出的增益控制因子。

4 結論

本文實現了一種全數字AGC的設計方案。此方案可實現40 dB動態范圍的控制,并且具有控制精度高,調節速度快,調試簡單,受環境影響小,穩定性和可靠性高等優點。隨著集成器件的發展,有望實現高動態范圍的全數字AGC,以便應用到更廣闊的領域中。

評論