基于CPLD的多次重觸發存儲測試系統設計

摘要:提出一種基于CPLD的多次重觸發存儲測試系統設計方案,詳細介紹系統硬件設計以及CPLD內部控制原理,并對CPLD控制電路仿真。該系統體積小、功耗低,能夠實時記錄多次重觸發信號,每次信號記錄均有負延遲,讀取出數據時,無需程序調整,即可準確復現記錄波形,因此重觸發技術在存儲測試系統中的應用具有重要意義。

關鍵詞:CPLD;多次重觸發;存儲;測試;波形仿真

1 引言

多次重觸發技術應用于多種場合,如一個30齒的齒輪,設齒輪嚙臺系數為1.2,若測量其中1齒多次嚙合時的應力,則1齒的嚙合時間只占齒輪轉l圈時間的1.2/30,其余28.8/30的時間為空閑態,而空閑態記錄無意義。為此開發多次重觸發技術,以齒應力作為內觸發信號,只記錄每次觸發后的有用信號,并具有負延遲,而不記錄空閑狀態.直到占滿記錄裝置存儲空間,這樣可有效利用存儲空間,記錄更多的有用信號。

2 多次重觸發存儲測試系統總體設計

2.1 多次重觸發存儲測試系統工作原理

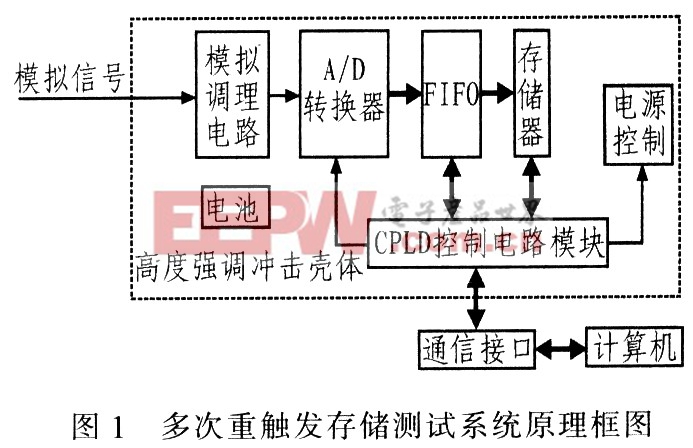

圖1為多次重觸發存儲測試系統原理框圖,其工作原理:被測信號經傳感器變為電信號后,輸入至模擬調理電路,再經放大濾波后輸入至A/D轉換器,將模擬信號轉換為數字信號,然后經過FIFO傳輸給存儲器,計算機通過通信接口讀取數據。其中,該存儲測試系統的A/D轉換器的轉換和讀時鐘、FIFO及存儲器的讀寫時鐘、推地址時鐘均由CPLD控制產生。

2.2 負延遲的實現

動態信息存儲要求真實有效地記錄有用信號,根據被測信號特點,需記錄下觸發前信號在極短時間內的數據,這就要使用負延遲技術。負延遲也稱為提前傳輸,即將觸發信號的觸發采集時刻提前一段時間作為傳輸數據的起始點。該系統設計采用FIFO存儲器實現負延負延遲。觸發信號未到來時,A/D轉換器輸出的數據不斷寫入FIFO存儲器中,A/D轉換器轉換的數據不斷刷新FIFO存儲器的內容。一旦觸發信號到來,數據則開始從FIFO寫入存儲器。

評論