基于FPGA快速A 律壓縮編碼的設計與實現

5驗證結果

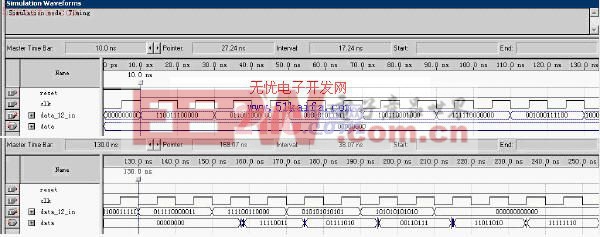

本文設計算法在quartusII 6.0開發平臺上,選用cyclone家族芯片對設計進行了功能、時序驗證[6],時序結果如下(圖5):

圖5 時序仿真結果圖

從圖5中可以看出,在clk=100MHz時鐘下,在第一個數據+1248(110011100000)輸入后,經過14個時鐘周期,輸出相應的帶極性的8位編碼為11110011,再第14個時鐘周期之后,隨后每兩個時鐘周期完成一組數據的壓縮編碼。這樣就實現了編碼的流水線作業,提高了數據處理效率。經過對數據的核對驗證,證明了數據運算的正確性,達到預計設計效果。

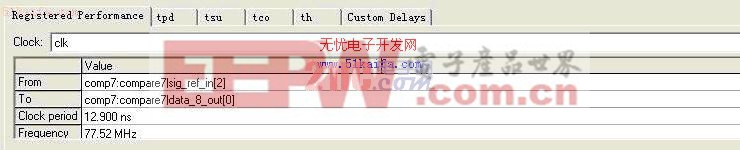

對系統進行運行速率評估,確定瓶頸通道如下圖6

圖6 時序分析圖

從圖5時序仿真圖可以知道,每兩個時鐘完成一組編碼,這是由于每個模塊完成數據處理需要讀寫兩個時鐘。從圖6可以看出,信號處理的最大時間消耗發生在comp7模塊內,耗時12.900ns,這意味著整個模塊的最大時間消耗為12.900ns。即有2T=12.900ns,計算出T=6.450ns,得出系統的最大時鐘頻率 =155.04MHz,最快編碼速率為77.52Mbyte/s。

6結束語

在實際語音通訊中,由于語音采樣速率相對比較低,一般編碼速率通常為64Kbit/s,在A律壓縮編碼中,使用本文提出的并行數據處理算法,應用VHDL實現了編碼的流水線操作,最快編碼速率為77.52Mbyte/s。因此,在多路信號采集中使用該算法可以極大的提高系統的工作效率。

評論