基于FPGA快速A 律壓縮編碼的設計與實現

3 編碼流水線算法設計思路

本設計從適合流水線操作的角度對常規算法[5]作了改進,前級完成相應位計算后將其結果傳遞到下一級,完成后進入下一組數據的編碼運算,從而達到流水作業的目的。由于每個模塊功能獨立,適合模塊化設計。

4 具體實現

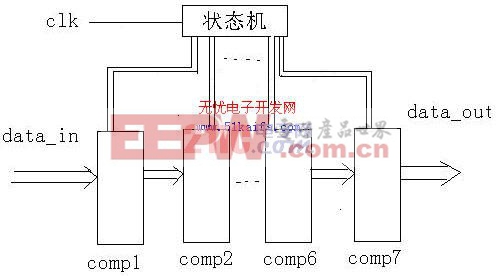

圖2 系統框圖

圖2系統框圖中實現了一種并行數據處理且適合于編碼流水線作業的改進算法,并采用FPGA具體實現。系統主要由狀態機(state)和比較單元(compare)這二部分組成,其中Comp1,Comp2,……Comp7這七個單元模塊在狀態機的控制下并行進行流水線數據處理。即在狀態機的控制下,在一個clk時鐘脈沖當中,七個單元同時進行著數據的處理工作,處理完成后,前一個Comp單元的輸出作為后一個Comp單元輸入,在下一個clk時鐘脈沖到來時緊接著又進行下一組數據處理。按照這種方式,依次處理下去,從而達到流水線作業的目的。下面對該系統進行具體實現。

評論