FPGA和ARM的Profibus-DP主站通信平臺設計

2.2.2 Scheduler和FDL_Controller狀態機

Scheduler狀態機功能塊負責實現對Slave_Handler狀態機的控制。它向Slave_Handler狀態機發送從站輪詢控制信號,控制其逐步與從站建立數據交換關系。

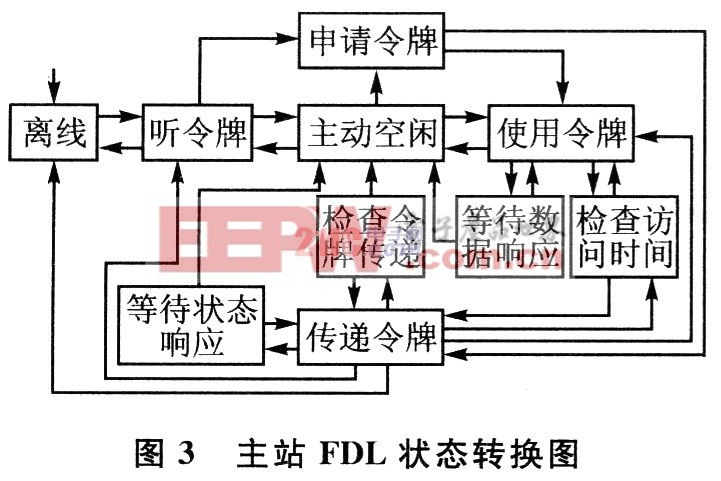

FDL_Controller狀態機由10個FDL狀態組成并在這些狀態間轉換,如圖3所示。本文引用地址:http://www.104case.com/article/191752.htm

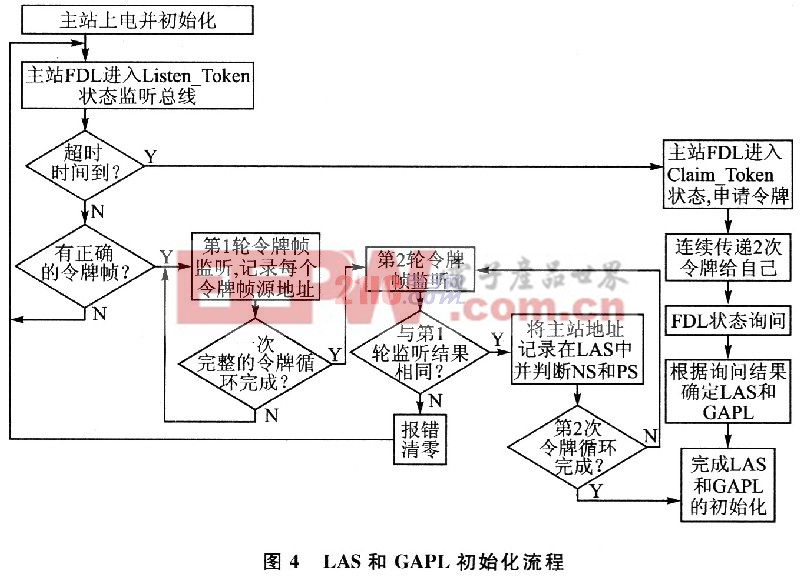

邏輯令牌環的建立主要工作是對LAS和GAPL的初始化。LAS和GAPL的具體初始化流程如圖4所示。

LAS的形成標志著邏輯令牌環初始化的完成。接下來就是邏輯令牌環運轉的維護階段,令牌將按照LAS進行循環傳遞,得到令牌的主站有權進行對其所屬從站的輪詢。傳遞過程中主站將以固定的時間間隔,通過Request FDLStatus主動幀來詢問自己GAP范圍內的所有地址,并根據詢問結果修改LAS和GAPL。在主站活動表生成之后,前驅站詢問ReqtJest FDL Starus,主站回復準備進入邏輯令牌環,并從Listen_Token狀態進入Active_Idle狀態(主站的前驅站會修改自己的GAP和LAS,并把該主站作為自己的后繼站)。主站在Active_Idle狀態監聽總線,能夠對尋址自己的主動幀作應答,但沒有發起總線活動的權力,直到前驅站傳送令牌給它,它保留令牌并進入Use_Token狀態,在此狀態下驅動Scheduler狀態機工作。主站持有令牌后,首先計算上次令牌獲得時刻到本次令牌獲得時刻經過的時間(即實際輪轉時間tRR),并與用戶設定的目標輪轉時間tTR比較,如果tRR小于tTR,則主站開始處理傳輸任務。首先處理高優先級傳輸服務,所有高優先級服務處理完畢后處理低優先級服務。在這個過程中,每一個完整的報文循環之后,主站就重新計算tTR―tTH。若結果小于0,主站進入PassToken狀態,將令牌傳遞給后繼站,未完成的任務留到下一次令牌持有的時候再執行。所有傳輸服務都完成后,不管是否有時間剩余,主站都交出令牌。如果主站接到令牌時發現tTR―tTHO,則只發送一個高優先級報文,完成后交出令牌。主站在令牌傳遞成功后,進入Active_Idle狀態,直到再次獲得令牌。

評論