基于FPGA的時間間隔測量模塊設(shè)計

2 系統(tǒng)硬件設(shè)計

系統(tǒng)硬件設(shè)計是整個系統(tǒng)的骨架,是數(shù)字電路設(shè)計的核心部件。所有程序代碼都在FPGA內(nèi)部運行,但是要使FPGA能夠正常運作,需要架構(gòu)一些基本的硬件支撐FPGA小型系統(tǒng)。

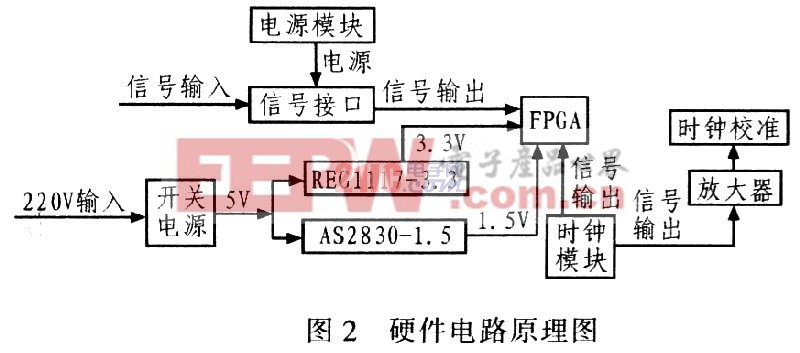

時間間隔測量系統(tǒng)的硬件設(shè)計主要包括:信號接口、電源、時鐘等模塊。

1)信號接口電路 信號接口電路主要用于接收外部輸入信號并進行電平轉(zhuǎn)換,以使協(xié)處理器得到穩(wěn)定電平的信號,起到保護協(xié)處理器的作用,并起到外部電壓波動的抗干擾作用。

2)電源 為使儀器直接與外部的市電220 V相接。這里外部電源采用開關(guān)電源220 V轉(zhuǎn)換5 V,內(nèi)部電源采用5 V轉(zhuǎn)換3.3 V電源模塊和5 V轉(zhuǎn)換1.5 V電源。整個儀器的內(nèi)部工作電壓為5 V、3.3 V和1.5 V 3種電壓模式。

3)時鐘 時鐘模塊是協(xié)處理器夠正常工作的保證,同時也是測量儀獲取時間間隔的重要依據(jù),本設(shè)計計數(shù)功能模塊采用脈沖計數(shù)法來獲取時間間隔,設(shè)計時需要考慮校準時鐘,以便定期對時鐘進行校準。

整個硬件電路原理設(shè)計如圖2所示。

3 系統(tǒng)軟件設(shè)計

測量模塊內(nèi)部需要的集成電路都是通過軟件來實現(xiàn),所以,先設(shè)計系統(tǒng)軟件流程計。其軟件設(shè)計包括:信號預(yù)處理、計數(shù)程序、總線控制器、鎖存器等模塊設(shè)計。

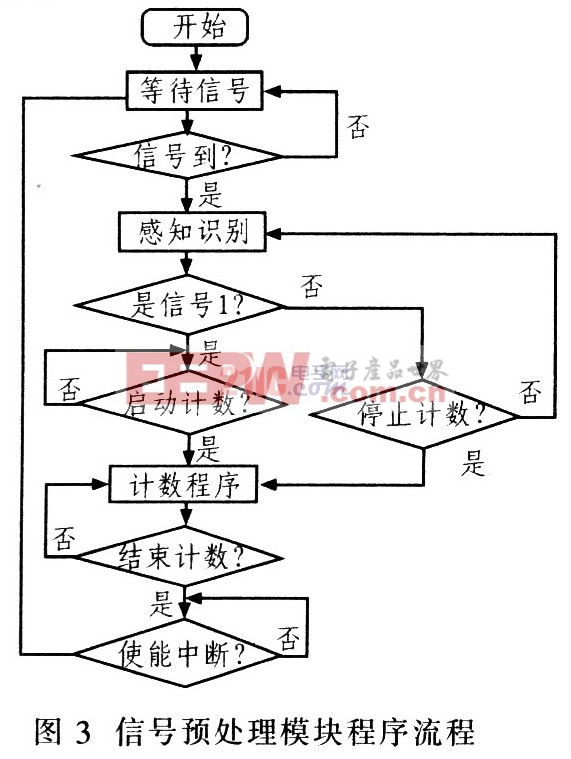

由于該系統(tǒng)軟件設(shè)計的4大模塊的設(shè)計過程類似,所以這里只介紹信號預(yù)處理模塊的設(shè)計流程及其后面的功能實現(xiàn)及仿真。

由于時間間隔測量儀在實際使用中可能會受到各種干擾,在靶場實際應(yīng)用中,經(jīng)常會存在蚊蟲干擾,沖擊波干擾,細小物體和外界光線的干擾,因此,需要在時間間隔測量儀的前端做濾波程序,但由于器件自身的特性及環(huán)境的復(fù)雜性,實際應(yīng)用中信號由光電靶傳輸?shù)綍r間間隔測量儀會存在誤跳變誤觸發(fā)現(xiàn)象,這種現(xiàn)象會導致時間間隔測量儀的誤判及誤測,針對這種異常現(xiàn)象,時間間隔測量儀可以模擬人的視覺來接收環(huán)境信息,并由神經(jīng)沖動進行信息傳遞,采取神經(jīng)網(wǎng)絡(luò)感知識別措施非常必要,識別程序流程如圖3所示。

啟動時間間隔測量儀,感覺器等待信號的到來,如果有信號,立即進行感知判斷,詢問是否為信號l,如果為信號1,則判斷是否啟動計數(shù),若計數(shù)程序正在執(zhí)行上一次信號的工作,則不啟動計數(shù)器,否則啟動計數(shù)器并發(fā)出中斷信號,發(fā)出開始信號,即使中斷置為高電平,通知主控制器準備讀取數(shù)據(jù),開始置為高電平。如果不是信號l,也就是當信號2到來時,則判斷是否停止計數(shù)器,如果信號2到來前未收到信號l,則感知程序可認為此時的信號2為無用信號,直接丟棄。如果信號2到來前已收到信號l,并已在計數(shù),但若小于預(yù)設(shè)的閘門關(guān)閉時間,則不關(guān)閉閘門,即中斷保持高電平不變,停止信號保持低電平。等待計數(shù)程序(計數(shù)模塊)結(jié)束發(fā)出復(fù)位信號,否則發(fā)出停止信號,即使停止置為高,計數(shù)器停止計數(shù)。若計數(shù)程序結(jié)束,則發(fā)出巾斷信號,使中斷置為低電平,進入下一步丁作。

評論