基于FPGA的DDS設計

5 DDS的FPGA實現

FPGA即現場可編程門陣列,它是作為專用集成電路領域中的一種半定制電路而出現的,既解決定制電路的不足,又克服原有可編程器件門電路有限的缺點。本設計采用Altera公司的Cvclone:II型器件。在實現DDS功能的同時,還能利用其中集成的Nios軟核進行控制模塊設計,加強集成度,減少器件使用和簡化電路設計。

本設計的軟件開發環境為Altera公司的Quartus II和Nios II IDE。

5.1 QuartusⅡ下的DDS設計仿真

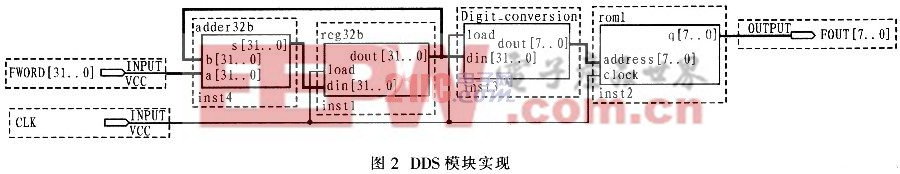

在Quartus II環境下利用VHDL語言對DDS內的寄存器、累加器及波形存儲器進行設計及仿真,最后鏈接生成DDS模塊,如圖2所示。

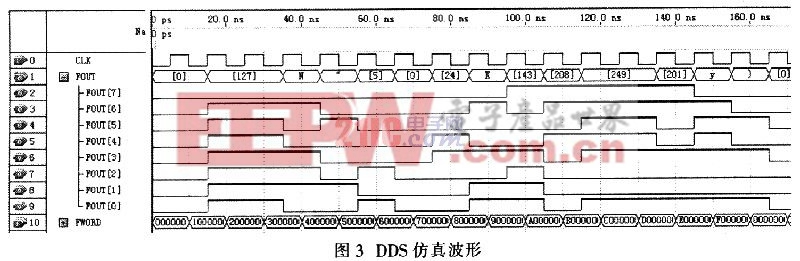

在檢查編譯文件后對DDS模塊進行仿真,仿真圖如圖3所示。至此在FPGA內已成功建立DDS模塊。根據所選用的具體器件內部存儲量的不同,可以根據自身需要更改ROM有效地址位數和ROM存儲波形的有效位數以提高系統的雜散抑制能力。

5.2軟核的硬件定制和軟件設計

利用Quartus II內的SOPC Builder工具完成Nios軟核內的CPU、Memory、I/O口等所需硬件定制。同時在NiosⅡIDE環境下運用C語言完成軟核內控制系統功能設計。

6 結束語

本文對直接數字頻率合成器結構、工作原理及DDS雜散分析進行了較深入研究,并在理論研究的基礎上結合Ahera公司的CycloneII器件完成了DDS的設計和實現。同時利用CyclonelI器件內的Nios軟核將DDS與控制系統模塊集成到一塊FPGA器件內,簡化設計難度,減小電路復雜程度。

評論