基于FPGA的DDS設計

2 DDS結構

2.1 相位累加器

相位累加器是DDS系統的核心,可完成DDS實現原理中的相位累加功能。為充分發揮DDS的優越性,一般累加器的位數都比較大,頻率字可控制DDS的輸出頻率,可根據需要設定。

2.2 波形查詢表

該電路的核心是一個查找表,查找表主要完成相位序列(相位碼)向幅度序列(幅度碼)的轉換。這里,用ROM構造一個查找表。如果把相位碼作為ROM的地址,只要在該地址中存儲相應的正弦幅度碼作為數據,就可通過相位碼尋址ROM,輸出信號函數。

2.3 D/A轉換器與低通濾波器

D/A轉換器和低通濾波器的作用是將幅度碼轉變成模擬信號。由于D/A轉換器輸出為階梯波,需通過低通濾波器取出其低頻成分(即DDS輸出)。

3 DDS頻率分析

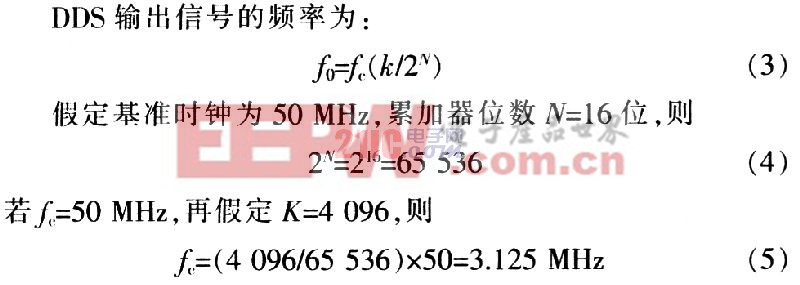

相位累加器在基準時鐘的作用下,進行線性相位累加,當相位累加器加滿時就會產生一次溢出,從而完成一個周期,這個周期也就是DDS信號的一個頻率周期。

可見,通過設定相位累加器位數、頻率控制字K和基準時鐘的值,可以產生任意頻率的輸出。DDS的頻率分辨率定義為:△fmin=fc/2N。

由于基準時鐘一般固定,因此相位累加器的位數即決定頻率分辨率。如果相位累加器為32位,那么頻率分辨率就可以認為是32位。位數越多,分頻率越高。只要N足夠大,即累加器有足夠的長度,總能得到所需的頻率分辨率。輸出頻率f0由頻率控制字K決定,即f0=K(fc/2N)。根據奈奎斯特采樣定理,DDS的最大輸出頻率f0Max應小于fc/2,在實際中,f0Max一般只能等于fc的40%。

4 DDS的雜散分析

DDS輸出頻率中的雜散信號是一個最重要的問題,而且是由于多種原因引起的。這里主要介紹以下3種原因:

1)電壓幅度截斷 幅度量化誤差,就是ROM存儲能力有限引起的舍位誤差,也可以認為是由D/A轉換器分辨率有限引起的誤差。參照相關數據資料,波形ROM的位數為D,由幅度量化誤差造成的輸出背景噪聲的單邊帶功率譜密度為:![]()

量化誤差引起的量化失真,可以用輸出信號與量化噪聲功率之比SQR來衡量。當D/A轉換器滿幅度輸出時,有![]()

式中,D是幅度量化的位數,D一定時,則噪聲的功率就一定。

2)相位截斷 由于ROM無法實現2N個地址單元的容量,因此截斷相位碼的高B位。主譜與最大的雜散幅度之比滿足如下關系:

式中,N為相位累加器的位數,B為相位截斷位數。

由上式可看出,由相位截斷引入的最強雜散相對主譜的電平由相位累加器輸出的有效位數決定:有效尋址位數每增加1位,雜散性能約提高6 dB。

3)D/A轉換器本身的問題 由于實際中D/A轉換器的非線性、瞬間毛刺等非理想轉換特性在輸出頻譜中會產生雜散。

評論