基于FPGA的電網(wǎng)實(shí)時(shí)數(shù)據(jù)采集與控制

3 A/D采集控制

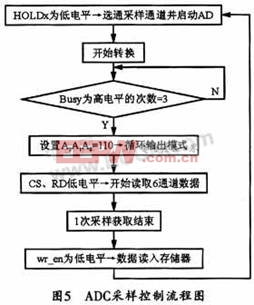

由于本設(shè)計(jì)要同時(shí)采集電網(wǎng)的三相電壓和電流,所以,應(yīng)把采樣倍頻信號接至HOLDA、HOLDB、HOLDC,以同時(shí)保持六路輸入信號,讀出模式設(shè)置為循環(huán)模式。

由ADS7864的時(shí)序圖可以得到如圖5所示的ADC控制器的軟件控制流程。以便在QuartusII開發(fā)平臺上利用VHDL語言進(jìn)行軟件編程。

通過ADS7864的工作狀態(tài)控制模塊可根據(jù)ADS7864的轉(zhuǎn)換時(shí)序圖,用VHDL編寫FPGA控制ADS7864的轉(zhuǎn)換程序,并可采用雙進(jìn)程有限狀態(tài)機(jī)的方法來在Quartus II 7.2內(nèi)對A/D控制模塊進(jìn)行時(shí)序仿真,其仿真波形如圖6所示。仿真結(jié)果表明,該模塊的設(shè)計(jì)完全符合要求。

4 結(jié)束語

本文給出了基于FPGA的電網(wǎng)實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法。該方法采用FPGA作為數(shù)據(jù)采集系統(tǒng)的控制核心。并充分利用了高速模數(shù)轉(zhuǎn)換芯片ADC和可編程邏輯控制器件FPGA,最終通過硬件描述語言VHDL實(shí)現(xiàn)了A/D的控制和數(shù)字鎖相倍頻電路。該電路具有良好的可移植性和可擴(kuò)展性,便于調(diào)試和修改,在電網(wǎng)的實(shí)時(shí)數(shù)據(jù)采集方面有較好的應(yīng)用前景。

評論