基于FPGA的電網(wǎng)實時數(shù)據(jù)采集與控制

2.1數(shù)字鎖相倍頻器的基本原理

輸入信號經(jīng)整形后可轉換為與輸入信號同頻率的方波信號,其頻率為FS,可對其進行K倍頻。首先設置一標準的時鐘信號,若時鐘頻率為FC,采用可編程分頻器對時鐘信號進行分頻,其分頻系數(shù)由計數(shù)器提供。若分頻系數(shù)為N,則輸出頻率為FC的N分頻,即:

時鐘信號經(jīng)K分頻后可送至計數(shù)器,由計數(shù)器在輸入信號的一個周期內對FC/K脈沖進行計數(shù),若忽略各種誤差因數(shù),其計數(shù)值為N,則:

由上兩式可得:F0=KFS,這樣就實現(xiàn)了對輸入信號頻率的K倍頻,倍頻后的信號即可作為A/D的采樣信號。數(shù)字鎖相倍頻器中計數(shù)器的實質是選用采樣窗口信號通過同步過程所得的方波信號作為閘門信號,并將高頻率的同步時鐘信號作為填充脈沖來進行計數(shù),設計數(shù)值為Ⅳ實現(xiàn)周期測量,由于該模塊在工作過程中可連續(xù)測量輸入信號的周期,所以兼有測頻的功能。因此,保證數(shù)字倍頻器跟蹤精度的關鍵是提高周期測量的精度和分頻系數(shù)的準確度。數(shù)字倍頻器的原理框圖如圖2所示。

2.2 數(shù)字鎖相倍頻的FPGA實現(xiàn)

輸入信號經(jīng)整形后也可轉換為與基波信號同頻率的方波,然后對方波信號進行二分頻。二分頻的目的有兩個,一是作為控制信號來實現(xiàn)周期測量;二是可以消除輸入波形不對稱的影響,提高測量周期的精度。將二分頻后的方波信號一路送K分頻器I的控制端,另一路反相后接K分頻器Ⅱ的控制端,以使兩路K分頻器在輸入信號相鄰兩個周期內交替處于分頻、清零狀態(tài)。這樣,兩路輪流工作就可避免使用單路計數(shù)器連續(xù)計數(shù)時由于數(shù)據(jù)保持和清零過程所造成的測量誤差和相位延遲問題。K分頻器在每次工作前,其輸出為0電平,這樣可以保證計數(shù)器的輸入方波與其計數(shù)周期同步,防止計數(shù)器輸入方波與計數(shù)周期的隨機性帶來的計數(shù)誤差,從而提高測量精度。本系統(tǒng)中,K取128。

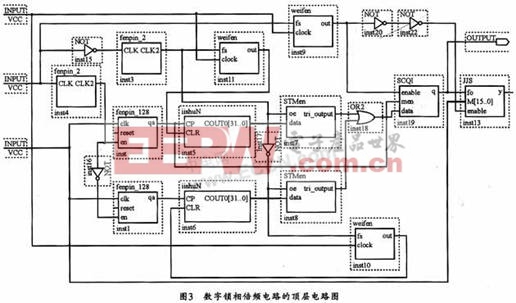

計數(shù)器的計數(shù)值N在被測周期結束后將立刻送鎖存器鎖存,并作為可編程分頻器的分頻系數(shù)N。由于采用兩路計數(shù)器輪流工作方式,因此,鎖存器要有選擇地對每路計數(shù)器的計數(shù)結果進行鎖存。考慮到要盡可能地減小相位滯后,在每個周期結束后,鎖存器應在最短的時間內將數(shù)據(jù)鎖存。這就要求鎖存器在鎖存脈沖到來前,先選擇好被鎖存的計數(shù)器,保證每個周期計數(shù)值的可靠鎖存。鎖存信號由輸入方波信號經(jīng)微分電路產(chǎn)生,這種設計使可編程分頻器在每個周期的開始時刻,總是以新的數(shù)據(jù)、新的起點開始分頻。兩路計數(shù)器在計數(shù)工作前要先清零,使計數(shù)器的計數(shù)值準確的反映輸入信號的周期。清零工作必須在計數(shù)結果鎖存后的下一次計數(shù)開始前完成。數(shù)字鎖相倍頻的頂層電路如圖3所示。

評論