基于FPGA的DDR內(nèi)存條的控制

摘要:隨著數(shù)據(jù)存儲量的日益加大以及存儲速度的加快,大容量的高速存儲變得越來越重要。內(nèi)存條既能滿足大容量的存儲又能滿足讀寫速度快的要求,這樣使得對內(nèi)存條控制的應用越來越廣泛。首先介紹了內(nèi)存條的工作原理,內(nèi)存條電路設計的注意事項,以及如何使用FPGA實現(xiàn)對DDR內(nèi)存條的控制,最后給出控制的仿真波形。

關鍵詞:FPGA;DDR內(nèi)存條;PCB電路設計

1 內(nèi)存條的工作原理

DDR內(nèi)存條是由多顆粒的DDR SDKAM芯片互連組成,DDR SDRAM是雙數(shù)據(jù)率同步動態(tài)隨機存儲器的縮寫。DDR SDRAM采用雙數(shù)據(jù)速率接口,也就是在時鐘的正沿或負沿都需要對數(shù)據(jù)進行采樣。在本設計中采用的內(nèi)存是hynix公司的lGB的HYMD564M646CP6-J。內(nèi)存條的工作原理與單顆粒內(nèi)存芯片的工作原理一樣,主要的控制信號以及控制信號完成的主要功能如表1所示。

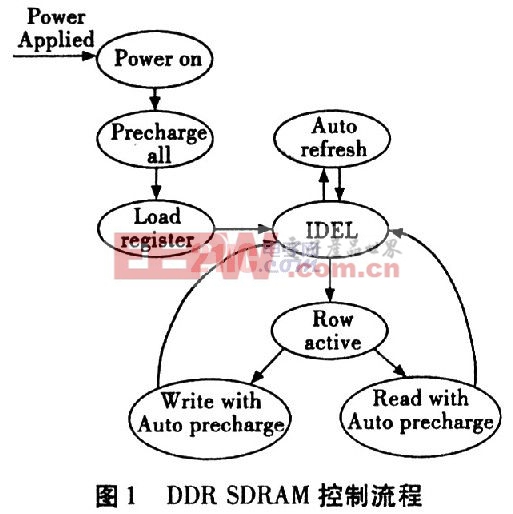

以上的控制信號及地址信號都是由差分時鐘信號中CK的正沿觸發(fā)。DDR SDRAM必須按照一定的工作模式來完成初始化,完成初始化后才能進入到讀寫過程。DDR SDRAM的控制流程如圖1所示。

評論