基于FPGA的Viterbi譯碼器設計

摘要:卷積碼及其Viterbi譯碼是現代通信系統中常用的一種信道編碼方法。文中介紹了Viterbi譯碼算法的原理,分析了Viterbi譯碼器的結構,然后用Verilog語言設計了一種基于Altera公司的EP3C120F780C8芯片的(2,l,7)Viterbi譯碼器,同時給出了時序仿真圖。

關鍵詞:卷積碼;Virelbi譯碼;FPGA

0 引言

在現代通信系統中,要使信號能夠更可靠地在信道中傳輸,往往需要我們在信道編碼中采用糾錯碼來降低信號受噪聲的影響,以降低傳輸的誤碼率。這種方法叫做差錯控制編碼或糾錯編碼,其思想是在發送端的信息碼元序列中增加一些監督碼元,這些監督碼與信碼之間有一定的關系,接收端可以利用這種關系由信道譯碼器來發現或糾正錯誤的碼元。

1 卷積碼

前向糾錯(FEC)是目前常用的一種差錯控制方法,在這種方法中,發送端發送能夠被糾錯的碼,接收端則在收到這些碼后,通過糾錯譯碼器來發現其中的錯誤并自動糾正接收碼字中的錯誤。在前向糾錯方法中,卷積碼及其Viterbi譯碼是常用的信道編碼方案。

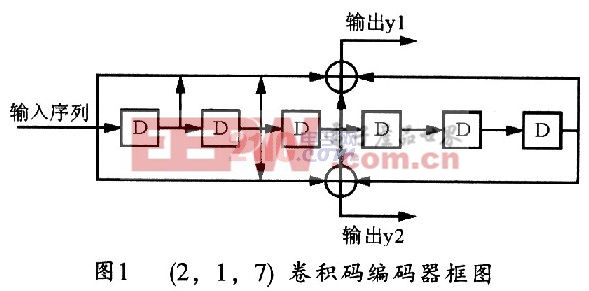

卷積碼通常用(n,k,N)表示,其中n為輸出信息比特,k為輸入信息比特,N為約束長度,卷積碼的編碼效率為Rc=k/n,圖1所示為(2,l,7)卷積碼的編碼器框圖。

(2,1,7)卷積碼編碼器由6個延時器(圖l中的D模塊,可用寄存器實現)和兩個模二加法器組成,它的編碼約束度為7,碼率為1/2。即輸入端輸入1比特信息,輸出端輸出2比特編碼信息,并分為上、下兩路并行輸出。

2 Viterbi譯碼器原理

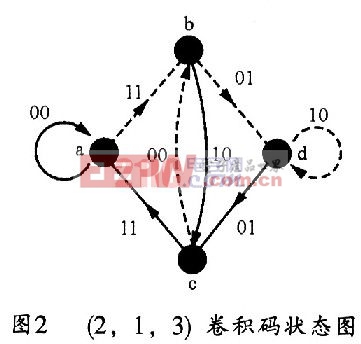

近年來,維特比算法具有很大的發展,目前在數字通信的前向糾錯系統中用的較多。Viterbi譯碼的基本原理是把已接收到的序列與所有可能的發送序列進行比較,選擇其中碼距最小的一個序列作為發送序列。下面以(2,1,3)卷積碼編碼器的編出碼為例,來說明Viterbi解碼的方法和過程。圖2所示是該碼的狀態圖。

評論