基于FPGA的RGB到YCrCb顏色空間轉換

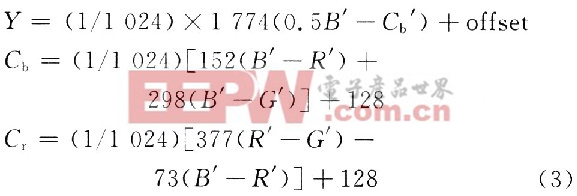

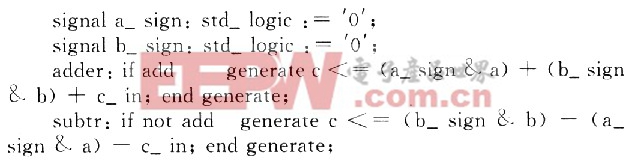

式中的除法運算可以通過截斷低位數據的方法實現,在截斷數據時,對截去小數部分判斷,采用4舍5入的方法,當截去部分的最高位是1時,有進位,最高位是0時,直接舍去。用VHDL語言描述式(3)的轉換算法,輸入R’,G’,B’是8位無符號二進制數,進行加減運算時,需要做符號位補位。本文引用地址:http://www.104case.com/article/191650.htm

在每個運算部件(包括乘法和加減法器)的輸出以及系統的輸入/輸出之間加上緩存寄存器,實現流水線設計。能提高資源利用率,加快運算速度,寄存器級數由運算延時大小決定。在輸出端用計數器控制運算開始時的噪音輸出。箝位電路控制輸出數據范圍滿足顏色空間的要求。

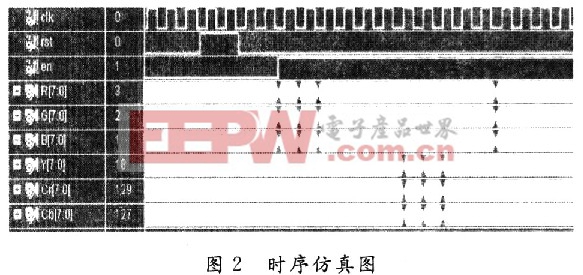

4 仿真結果

在xilinx的Virtex4-FX平臺實現現圖1的電路結構,用ISE軟件仿真。資源使用情況如下:

時序仿真結果如圖2所示。

通過圖2可以驗證轉換算法的正確性。在使能信號en有效后,經過6個時鐘的運算時延,輸出端有轉換結果輸出,輸出結果四舍五入,誤差為O.5,比以往算法提高了變換結果的精度。

5 結語

通過對轉換算法的研究,推導出適合在FPGA上實現的新算法,算法優點突出。算式中乘法器采用DSP48 Slice模塊實現,提高了轉換算法的運算速度。從綜合報告可以看出,除了使用5個DSP48s外,其他資源使用的比較少。運算速度最大能夠達到189 MHz,能夠充分滿足運算量大,實時性要求高的應用。

評論