基于FPGA的RGB到YCrCb顏色空間轉換

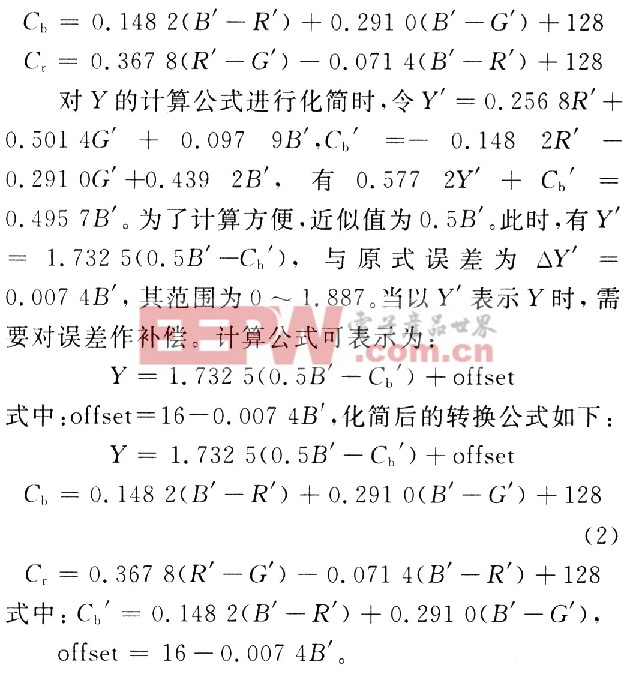

根據B’的取值不同,ofset的取值取整后為14,15,16。在計算過程中,可以用一個數據選擇器根據B’值的不同選擇offset的值。0.5-B’的計算可以用移位實現。化簡后的轉換算法.對Y,Cb,Cr的計算將比原來節省4個乘法器。在FPGA中,加法器、數據選擇器和移位算法的實現比乘法器簡單,該化簡將利于減少邏輯資源的應用,簡化實現電路,提高運算速度。轉換電路結構如圖l所示。本文引用地址:http://www.104case.com/article/191650.htm

3 基于FPGA的實現

在FPGA中,對乘法的實現比較復雜,可以采用如下幾種方法:

(1)直接用編程語言描述乘法運算,由綜合工具自動實現,用該方法描述,實現簡單,但是耗用比較多的邏輯資源。

(2)利用查找表的方式實現乘法運算,事先把要相乘數據的所有結果算出來存到ROM中,根據輸入數據的值讀取相應的結果,當用該方法相乘數據位數比較多時,會占用大量的存儲空間。

(3)用FPGA中內嵌的乘法器實現,該方法實現簡單,當用VHDL語言實現時,調用相應的乘法模塊即可。

本文采用第三種方法,用專用乘法器來實現轉換公式中的乘法運算。Xilinx的Virtex 4系列FPGA芯片內嵌的乘法器為Xtreme DSPTM S1i-ceDSP48 Slice其工作頻率高達500 MHz,支持多種獨立的功能,包括乘法器、乘累加器(MAC)、后接加法器的乘法器、三輸入加法器、桶形移位寄存器、寬路線多路復用器、大小及比較器或寬計數器。本文將運用DSP48 Slice模塊實現乘加運算,在電路結構圖的虛線框中,乘法和加法的運算將用單個DSP48 Slice模塊實現。這樣將會減少轉換關系式中加法器的數量,節約邏輯資源,在程序中可以用元件例化語句調用DSP-48 Slice模塊,實現方法簡單,程序簡潔。為了滿足浮點數和運算精度的要求,適合在FPGA中實現,將式(2)改寫為:

評論