基于FPGA的PPM調(diào)制解調(diào)系統(tǒng)設(shè)計

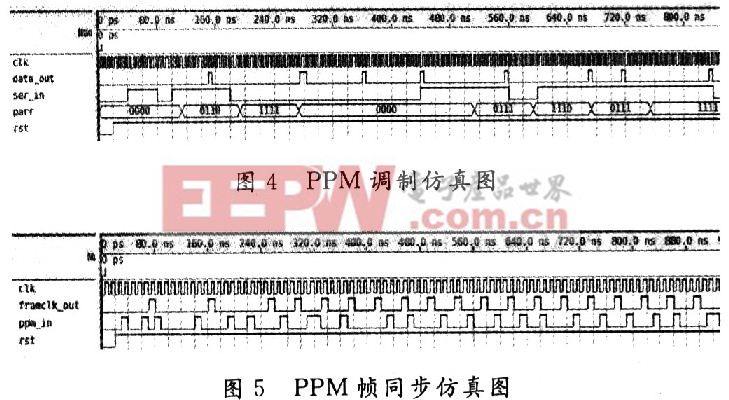

整個系統(tǒng)在Quartus 8.0平臺進行仿真,圖4為PPM調(diào)制仿真圖。ser_in為串行輸入的數(shù)據(jù),parr為串/并轉(zhuǎn)換后的并行數(shù)據(jù),data_out即為PPM調(diào)制后的輸出信號,從圖中可以看到PPM調(diào)制正確。為了更好地展現(xiàn)程序逐漸同步的原理,選擇從4-PPM信號中恢復(fù)幀同步,如圖5所示,從仿真中,不難看出幀同步輸出framclk_out逐漸同步的過程。本文引用地址:http://www.104case.com/article/191649.htm

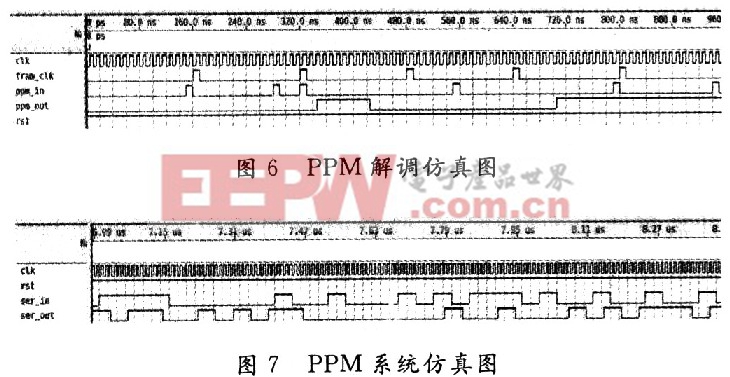

圖6為PPM解調(diào)仿真圖,圖7為系統(tǒng)整體仿真,即串行輸入數(shù)據(jù)經(jīng)PPM調(diào)制后,解調(diào)程序從已調(diào)信號中提取幀同步,并解調(diào)出原有串行輸入數(shù)據(jù),從圖7中看到串行輸入數(shù)據(jù)與串行輸出數(shù)據(jù)之間存在一定的延遲,一方面是因為硬件系統(tǒng)自身存在延遲,更主要的原因是由于在PPM調(diào)制時,比較器需等待第一次串/并轉(zhuǎn)換完成再進行比較,并輸出PPM信號,而解調(diào)是在基于調(diào)制后PPM信號進行的,從而導致了仿真中的延遲,但在實際運用中這個延遲并不存在。

5 結(jié)語

用Verilog HDL語言設(shè)計完成了基于FPGA的PPM調(diào)制解調(diào)系統(tǒng),并在Quartus 8平臺上對調(diào)制過程、幀同步過程和解調(diào)過程以及整個系統(tǒng)進行功能仿真和時序仿真,從仿真中可以看出整個系統(tǒng)達到了預(yù)期的目標,能夠高效穩(wěn)定地完成PPM調(diào)制與解調(diào)過程,為將來的實用化打下了基礎(chǔ)。但另一方面,也在仿真中發(fā)現(xiàn)幀同步時間偏長,需要進一步改進。

評論