高速突發模式誤碼測試儀的FPGA實現方案

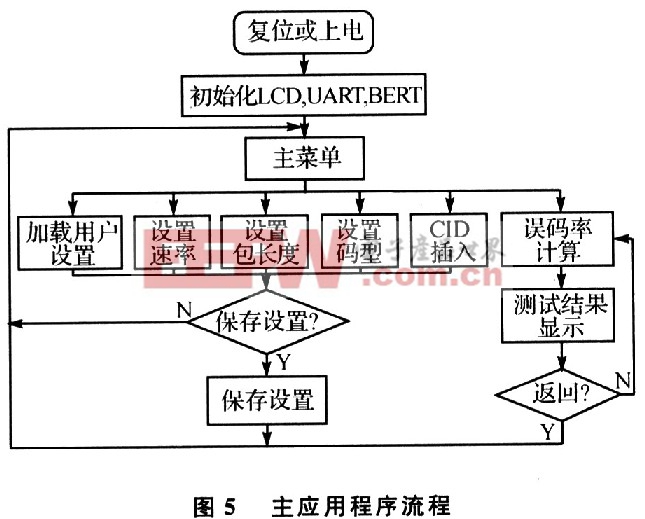

控制程序包含的函數主要有GPIO驅動、UART驅動、LCD驅動、GTP DRP屬性的讀改寫函數、BERT的控制和狀態讀取函數、誤碼率計算函數、主函數等。主函數提供一個用戶與誤碼測試儀交互的平臺,其流程如圖5所示。本文引用地址:http://www.104case.com/article/191631.htm

在上電或復位后,系統初始化LCD和UART,并加載上次保存的用戶設置以初始化BERT。然后進入主菜單,主菜單上可以通過選擇相應選項進入相應的操作。通過讀取誤碼測試加載的上次保存的用戶設置,核對本次用戶需要的設置是否與上次保存的設置相同,如果不同可以返回主菜單,從主菜單進入相應的設置操作,進行參數的修改。修改完畢后,如果用戶要保存本次設置,可以進行保存再返回主界面;如果不需要保存,則直接返回主界面。從主界面上可以選擇誤碼測試顯示進入誤碼測試結果顯示界面,在顯示誤碼測試結果前,控制程序會先進行計算誤碼率,以保證實時顯示誤碼測試結果。

4 系統驗證與設計總結

為了驗證系統的性能,分別用該儀器做了自環測試和對1.25 GHz GPON系統突發式光接收模塊的誤碼測試。在自環測試中,發送的數據不通過光路直接送到BMCDR的接收端。測試結果表明,在電信號信道中誤碼測試系統自身不會誤碼。在對1.25 GHz GPON系統突發式光接收模塊測試過程中,采用兩個步驟的測試。步驟1中,按圖1連接誤碼測試系統,兩路數據包信號0UN#1和0UN#2都不經過可變光衰減器的衰減,經光合路器合路后的光信號中所有包信號幅值一致,用以驗證誤碼測試系統光路中是否產生誤碼,實驗結果同樣驗證了誤碼測試系統自身不會產生誤碼。步驟2中,對一路數據包信號進行不同幅度的衰減,使光合路器輸出的光信號存在幅值的跳變,并在兩路數據包信號存在不同幅值跳變的情況下,分別測試突發式光接收模塊的誤碼性能。試驗中使用的被測突發式光接收模塊強包弱包幅度相差20 dB,保護時間為32位,速率為1.248 8 Gbps的情況下誤碼率低于10-12。,說明此誤碼測試系統具有較好的性能。

評論