高速突發模式誤碼測試儀的FPGA實現方案

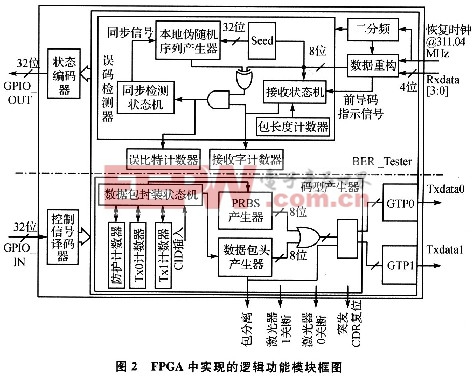

2 FPGA中邏輯功能模塊設計

作為實現突發模式誤碼測試儀的重要芯片,FPGA主要實現如下功能:

①發送端產生兩路高速的時分復用信號,這兩路信號要具有GPON上行數據包的特點,即32位保護時間,44位前導碼,20位定界符。

②接收部分將接收到的4位寬的數據并化為8位寬的數據,并搜尋定界符將接收的數據進行邊界對齊。

③誤碼檢測器將接收到的邊界對齊后的數據與本地產生的偽隨機碼進行比對,僅對有效數據中出現的誤碼進行統計。

④同步檢測,失步后的重新同步。

圖2為FPGA中實現的主要邏輯功能模塊。

①控制信號譯碼器根據Microblaze微處理器通過GPIO_IN輸入的地址信息,將控制信息賦值給誤碼測試邏輯模塊相應的控制信號。控制信息主要包括:包長度、保護時間長度、前導碼長度、碼型選擇、GTP屬性的DRP地址和值、時鐘合成芯片的控制信息等。

②狀態編碼器將誤碼測試模塊的狀態信息存儲映射到不同地址的GPIO_OUT上,然后傳送給Microblaze微處理器。輸出的狀態信息主要包括:誤碼比特數、接收到的總碼數、同步狀態、接收無信號等。

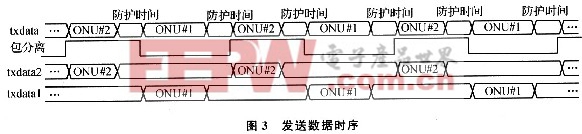

③碼型產生器模塊包含PRBS產生器和數據包頭產生器2個子模塊。PRBS產生器根據碼型選擇控制信號產生相應碼型的8位寬度偽隨機序列,數據包頭產生器模擬GPON上行數據包包頭結構的特點中產生類似前導碼和定界符的碼型。碼型產生器模塊還包含1個數據包封裝有限狀態機,它的主要作用是產生發送碼狀態的控制信號,將包頭數據、包間隔(保護時間)、CID(長連O/1)穿插在PRBS中以模擬GPON上行數據。包含兩路包信號的數據txdata在與包分離信號相與后,分離成兩路時分復用的信號txdata0和txdatal,時序如圖3所示。

④GTP0和GTPl為FPGA芯片的固核。它將低速的8位寬度的并行數據txdatal和txdata2串化為1路高速的串行數據,可以通過修改GTP的DRP屬性來改變發送數據的速率。GTP還負責向發送端提供同步時鐘。

⑤數據重構模塊將接收到的4位寬的數據并化為8位寬的數據,并搜尋16位定界符將接收的數據進行邊界對齊。

⑥誤碼檢測器主要由1個本地偽隨機序列產生器、1個接收狀態機和1個同步檢測狀態機構成。本地偽隨機序列產生器與發送端的隨機序列產生器階數和本原多項式相同,它生成的偽隨機數據與接收到的數據進行比對,對比的結果由誤碼計數器進行統計。接收狀態機根據定界符檢測信號和包長(包1或包2)計數器來判斷接收的數據是否為有效數據,并生成一個有效數據指示信號。同步檢測狀態機根據比對結果判斷本地隨機序列產生器生成的數據與接收到的數據是否已經同步,如果沒有同步,本地偽隨機序列產生器將從接收的數據中截取32位的連續信號作為其移位寄存器的初始值來產生后面的數據以重新同步(灌碼同步)。

⑦誤比特計數器用來統計誤比特數,它僅對有效數據中出現的誤碼進行統計。接收字計數器用來統計接收到的有效數據字節數。

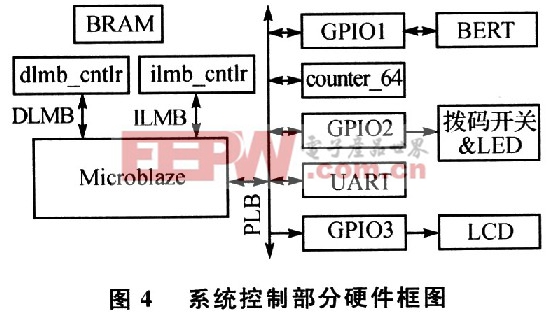

3 控制系統設計

本設計中使用Microblaze嵌入式軟核處理器來實現對誤碼測試儀邏輯部分的控制,控制部分的硬件框圖如圖4所示。GPIO1用于處理器與BERT核的通信;GPIO2與LED和撥碼開關相連,用于顯示狀態和板級控制誤碼測試儀;GPl03與LCD相連,將誤碼測試結果顯示于LCD上;count-er 64為64位寬的計數器,用于記時。UART通過RS232與電腦相連,讀取在PC上設定的控制信息并將誤碼測試結果和誤碼儀的狀態詳細地顯示在PC上。

評論