基于FPGA的信道化接收機(jī)

現(xiàn)代電子戰(zhàn)場的電磁環(huán)境復(fù)雜多變,信號環(huán)境朝著密集化、復(fù)雜化、占用電磁頻譜寬帶化的方向發(fā)展。另一方面,采用陣列天線對接收信號進(jìn)行信號參數(shù)估計,是電子偵察系統(tǒng)中常規(guī)的技術(shù)手段之一。因此,寬帶陣列接收系統(tǒng)有著廣泛的應(yīng)用前景。傳統(tǒng)的寬帶陣列接收機(jī)用多臺單通道接收機(jī)并行工作,并行的同時接收不同頻點(diǎn)上的信號來達(dá)到全頻域覆蓋的目的,也可以用多通道接收機(jī)多個通道并行同步的工作來實(shí)現(xiàn),前者增加了系統(tǒng)成本和讓整個并行系統(tǒng)同步工作的復(fù)雜度,后者當(dāng)信道數(shù)比較大和指標(biāo)要求比較高時,信號處理的復(fù)雜度和器件實(shí)現(xiàn)的可行性要求很高。基于多相濾波的數(shù)字信道化陣列接收機(jī)在通信類電子戰(zhàn)中對跳頻信號的快速搜索以及雷達(dá)對抗中對捷變頻雷達(dá)信號的全概率截獲等表現(xiàn)出很高的潛在研究和應(yīng)用價值。

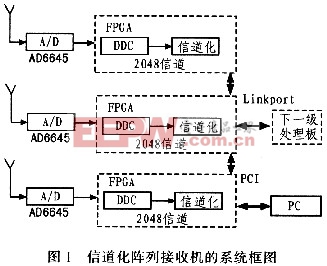

1 系統(tǒng)組成

該系統(tǒng)設(shè)計是基于多相濾波的信道化原理,對寬帶陣列接收機(jī)進(jìn)行設(shè)計,實(shí)現(xiàn)在單板上同時處理3路中頻70 MHz,帶寬30 MHz的模擬信號,其中子信道帶寬僅25 kHz,有利于后端模塊進(jìn)行精細(xì)化信號分選和處理,信道化多相因子為8。帶外抑制大于55 dB。系統(tǒng)還可以將陣列中某一路子信道數(shù)據(jù)通過PCI接口上傳到PC機(jī)顯示信道化結(jié)果。系統(tǒng)具有完善的時鐘方案,多板連接時,可達(dá)到陣列天線的同步要求。另外,由于系統(tǒng)大部分?jǐn)?shù)字信號處理都是在FPGA中完成,所以整個系統(tǒng)具有功耗小、體積小、成本低、操作靈活的特點(diǎn)。圖l為信道化陣列接收機(jī)的系統(tǒng)框圖。

2 硬件電路設(shè)計

該中頻數(shù)字接收機(jī)的硬件設(shè)計原理圖如圖2所示。中頻信號經(jīng)過單端轉(zhuǎn)差分電路以差分信號形式輸入到模數(shù)轉(zhuǎn)換器,AD6645將模擬信號轉(zhuǎn)換成數(shù)字信號送入FPGA中進(jìn)行處理,其中一片的處理結(jié)果通過PCI上傳到PC機(jī)顯示,兩片時鐘分配器件分別提供系統(tǒng)需要的多路單端和差分時鐘。

評論