基于FPGA和SMT387的SAR數據采集與存儲系統

合成孔徑雷達(SAR)是主動式微波成像雷達,近年來隨著合成孔徑雷達的高速發展,對作為重要部分的數據采集和存儲系統的要求越來越高,比如對數據采集系統的采樣率、分辨率、存儲深度、數字信號處理速度、抗干擾能力等方面提出更高要求。基于標準總線并帶有高速DSP的高速數據采集板卡和利用高速A/D轉換器搭建的數據采集系統是超高速數據采集技術目前兩大主流發展方向。SAR系統的數據采集和存儲處理需要滿足正交兩路(I/Q)雷達回波信號數據同時采集,并實現高速傳輸和大容量長時間實時存儲。根據這一要求,結合采集存儲的發展趨勢,設計并實現了一種應用于SAR,基于SATA硬盤的高速數據采集和存儲系統。采用FPGA實現系統工作時序控制,DSP功能模塊完成信號的

處理和對硬盤的操作。該系統能夠實現脫機,長時間,高速大容量的數據存儲。

1 系統構成及設計原理

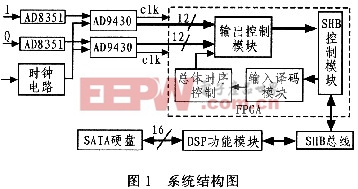

本系統由模數轉換模塊、采集存儲控制模塊、DSP功能模塊和數據存儲器(硬盤)組成。其中模數轉換模塊和采集存儲控制模塊位于電路板1,數據存儲接口模塊位于電路板2,板間按照SHB接口協議通信。系統實現思路為:首先采集正交輸出的I/O兩路模擬正交信號,經過并在雷達回波有效時間內將數據送入DSP功能模塊轉化數據格式。在兩次回波有效窗的間隔時間內,將數據存入SATA硬盤中,系統結構如圖l所示。

1.1 數據采集模塊

模數轉換模塊主要功能是:在120 MHz的采樣時鐘下,將I/O兩路模擬正交信號轉換成12位數字信號,送給后端的采集存儲控制模塊。該模塊由信號調理器和A/D轉換器2部分構成。信號調理器主要完成對輸入信號的幅度和共模電壓的調整,A/D轉換器將調整后的模擬信號均勻采樣得到其量化的數字信號。根據系統要求,運算放大器選用AD8351,該器件是用于RF和IF頻段的低功耗差分運放,其輸出放大增益和差分共模電壓均可通過調整片外相應電阻阻值實現。A/D轉換器選用AD9430,該器件分辨率為12位,最高轉換速度為170百萬次/秒,輸入信號模擬帶寬為710 MHz,輸出模式可靈活配置。

1.2 采集存儲控制模塊

采集存儲控制模塊是整個系統運行控制的核心部分之一,其內部框圖如圖1的FPGA部分。該采集控制模塊的主要功能是:前端采集的數字信號在輸出控制模塊的控制下(編碼等處理),經SHB送到DSP功能模塊,DSP通過基于紐曼-皮爾遜準則的滑窗檢測算法計算出有效信號的具體

位置,并得到這些參數(CalEnd、Start、Hold、Error、Pause、Delay、CalPRF、PRF-INCRS和Full),然后經過編碼將這些參數傳送給采集控制模塊,采集控制模塊通過譯碼模塊,恢復這些參數并通過這些參數控制時序,就可以采集信號的有效部分。最后通過SHB把這些有效信號傳給DSP功能模塊,存儲在SATA硬盤中。該采集存儲控制模塊的時鐘為120 MHz。

根據設計要求,采集存儲控制模塊的最高工作頻率為240 MHz,由于該模塊的主要功能是對系統中各子模塊的接口連接和控制,所以其外部接口較多,還涉及到多電平模式間的轉換和兼容。通過最后的仿真綜合分析,本方案設計選用Virtex 4系列的FPGA器件XC4VFXl2。

如圖1中的FPGA框圖,采集存儲控制模塊包括4個主要的功能模塊,其中總體時序控制模塊是核心模塊。按照系統工作要求,本系統設計并實現了如下工作:系統開機后,外部硬件電路將對系統進行自動復位。復位信號有效后,總體時序控制部分將進人狀態“0001”,對總體時序控制所有參數進行初始化配置。參數配置結束后,將自動從狀態“0001”跳轉至狀態“0010”。狀態“0010”是總體時序控制部分的狀態跳轉中樞,該狀態根據譯碼產生的控制信號跳轉至相應的下一個工作狀態。根據系統工作方案,需要FPGA在接收到START(開始傳送數據)信號后,向后端傳送單個完整的PRI內的采樣信號。此時CalEnd信號為系統初始化時,所賦予的初始值‘0’。當FPGA接收到START信號后,將檢測CalEnd是否為其初始值‘0’,當條件“CalEnd=‘0’and START=‘1’”成立時,總體時序控制部分將從狀態“0010”跳轉至狀態“001 1”。總體時序控制部分跳轉至“0011”狀態后,將在下一個PRF上升沿到來后,通過PCI輸出管理部分開啟SHB輸出通道,傳送一個完整PRI內的采樣數據。數據傳送完畢后,自動由狀態“0011”跳轉回狀態“0010”,并關閉SHB輸出通道。至此,FPGA對計算結束前接收的一次START命令執行完畢。當信號檢測部分一旦檢測到有效回波位未能完整落入采樣PRI內時,將通過SHB輸入端口向FPGA傳送DEIAY信號。在總體時序控制部分接收到輸入信號譯碼產生的DElAY信號后,將在下一個PRF上升沿到來后,由狀態“0010”跳轉至狀態“0100”,當延時完成后自動由狀態“0100”跳轉回狀態“0010”。當信號檢測結束后,后端模塊將通過SHB輸入單元把PRF延遲量傳送至FPGA,同時將總體時序控制中的Ca-lEnd信號置高。當總體時序控制部分檢測到CalEnd信號為高時,將在下一個PRF上升沿到來后,由狀態“0010”跳轉至狀態“0101”。在狀態“0101”中,根據計算的PRF延遲結果,對采樣PRF的位置進行一次延遲。延遲結束后,將自動跳轉至狀態“0110”。狀態“0110”中。總體時序控制部分將通過SHB輸出控制模塊關閉SHB通道。同時等待數據傳送開始信號START。

評論