基于FPGA的高速寬帶跳頻發射機的中頻設計

摘要:結合軟件無線電思想和架構,利用Altera EP3C16F4 84C6作為中頻信號處理器,設計了一種基于統一硬件架構的數字化高速寬帶跳頻發射機,實現跳頻速率125kHops/s,跳頻帶寬320MHz。

本文引用地址:http://www.104case.com/article/191476.htm引言

跳頻通信是在惡劣的電磁環境中保證正常通信的主要手段。提高跳頻通信系統的跳頻速率和跳頻帶寬可以有利于對抗單頻窄帶干擾,頻帶阻塞干擾以及跟蹤干擾,是提高跳頻通信系統抗干擾能力的主要手段。

傳統的跳頻發射機是通過模擬本振的跳變或切換來實現跳頻的功能。采用模擬本振跳變的方案跳頻速率受本振頻率切換速率的影響;采用本振切換的方案,至少需要兩個模擬本振和一個高速模擬開關進行乒乓切換,外圍電路較復雜,且靈活性較差。本文根據軟件無線電的設計思想,將基帶調制,數字上變頻,以及跳頻控制用數字化的形式在FPGA內部實現,只需通過改變FPGA內部數控振蕩器的輸出頻率就可以實現高速寬帶跳頻。這樣避免了模擬本振的高速跳變,提高了跳頻速率,簡化了系統硬件結構,同時還增強了系統的靈活性。

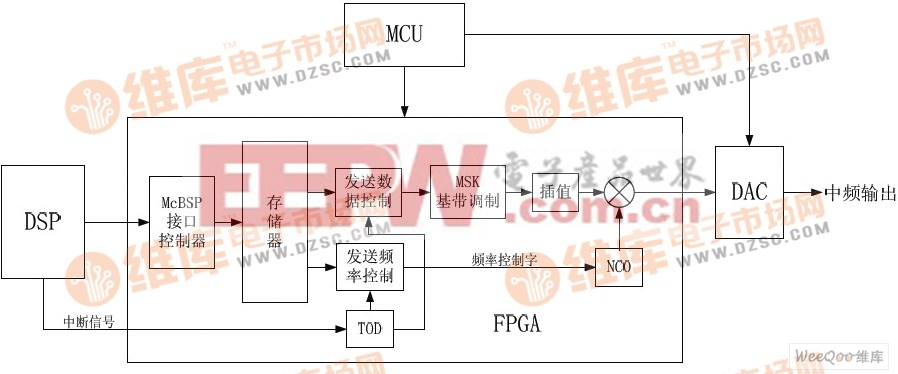

本方案采用EP3C16F4 84C6作為跳頻發射機的中頻信號處理器,其處理能力最高可達幾十吉乘累加運算,并且具有最高可達840Mbps的高速LVDS接口。DA轉換器采用AD9736,具有14bit精度,1.2GSPS轉換速率。該高速寬帶跳頻發射機具有高度靈活性,其中跳頻圖案,跳頻數,跳時,以及發送消息等參數由DSP實時生成。并對FPGA進行配置。系統整體結構如圖 1所示:

圖 1 系統結構框圖

2 FPGA設計與實現

2.1 存儲器設計

FPGA內部存儲器用于與DSP進行數據交換。存儲器分為:發送消息存儲區,發送頻率控制字存儲區,跳時寄存器,跳頻數寄存器。地址分配如表1所示:

表1 FPGA內部存儲器分配表

2.2 MSK調制

2.2.1 通用調制模型

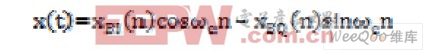

軟件無線電調制技術要求能夠在通用的數字信號處理平臺上,實現多種不同體制的調制方法,這就需要設計出一種通用的調制器結構。正交調制一般可以用式1表示:

其中 為基帶信號的同相分量和正交分量,它們是由調制方式決定的。

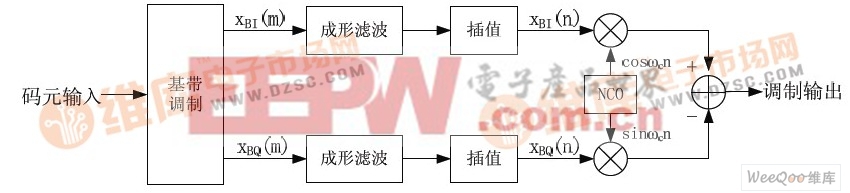

為基帶信號的同相分量和正交分量,它們是由調制方式決定的。 為載波的角頻率。根據上式,我們可以得出正交調制的實現結構如圖2所示:

為載波的角頻率。根據上式,我們可以得出正交調制的實現結構如圖2所示:

圖 2 正交調制原理框圖

基帶調制根據不同的調制方式選擇不同的方法。成形濾波用來抑制頻譜的旁瓣,以達到特定的頻譜帶寬要求。插值用來進行采樣率變換,使得數據速率與NCO輸出數據速率相同,進行載波調制。最后取IQ兩路復信號的實部輸出即得中頻已調信號。

評論