應對FPGA/SDI子系統中的高速板布局挑戰

•將跡線阻抗設為75±10%、100±10%

•使用最小的表面貼裝元件和最小的無源元件接合焊盤

•選擇能最大限度減少信號路徑上阻抗失配的跡線寬度

•選擇支持單獨接地基準75單端跡線和100寬松耦合差分跡線的板堆疊

•使用表面貼裝陶瓷電容器和射頻信號電感器

•使對回波損耗有影響的元件(終端電阻器、阻抗平衡網絡)盡可能接近集成電路針腳

•使用75受控阻抗,設計良好的BNC布局

•保持互補信號發送的對稱性

•均勻地傳送100差分跡線(使跡線上的跡線寬度和跡線間隔保持均勻)

•避免陡彎,使用45度彎曲

•遵循信號路徑識別幾何變化,并預估相應的阻抗變化

•使用整平面。如果需要采用凹凸地面抵消過多的寄生電容,應謹慎使用;借助三維仿真工具決定布局

•使用最短的VCC和接地路徑,將針腳連接到通孔面

布局示例

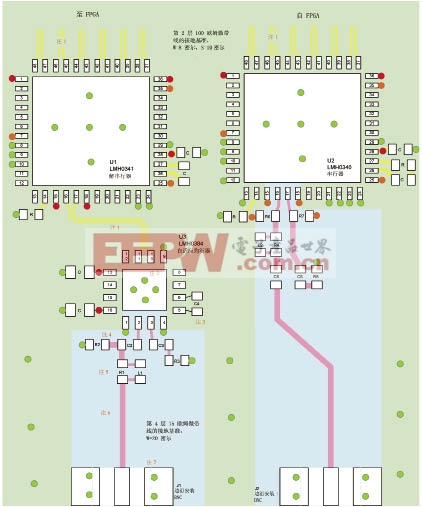

圖9是美國國家半導體LMH03843Gbps/HD/SDSDI自適應電纜均衡器、LMH0341SDI解串行器、LMH0340SDI串行器和FPGA(未顯示)的簡要布局圖。本例使用圖4中顯示的堆疊。第2層(綠色顯示)是8密爾寬100差分跡線的接地基準,它連接到LMH0384的輸出針腳SDO+和SDO-以及LMH0340和LMH0341的LVDS信號傳送線。第4層上的金屬島(藍色顯示)用作75跡線的接地面。這兩個接地基準使用設備DAP連接通過地面縫合到一起。

圖9 LMH0384、LMH0340和LMH0341的布局示例

交流耦合電容器C2緊鄰SDI+的輸入針腳。阻抗匹配網絡L1和R1通過C2盡可能地靠近輸入針腳SDI+。75終端電阻器R2置于C2后方,以最大限度減小接線柱的影響。

這種設計使用0402尺寸元件,盡可能減少75跡線的阻抗變化,75跡線通過20密爾微帶線連接到第4層基準。BNC使用的布局應具有良好的信號發送,以實現低回波損耗。

圖9注釋如下:

注1-使用100差分阻抗連接到第2層基準的耦合跡線。

注2-第2和第4層的接地縫合。

注3-C4鄰近集成電路針腳。

注4-C2盡量靠近集成電路輸入針腳;R275接收端子置于C2后方。

注5-L1、R1阻抗匹配網絡通過C2鄰近SDI+針腳。

注6-使用75受控阻抗跡線連接到第4層基準。使用0402元件。使用15-25密爾的跡線寬度,以最大限度減少較大元件焊盤導致的阻抗降。

注7-BNC使用75受控阻抗布局。

總結

SDI板布局的難點在于設計一種方案,可以最大限度減少75端口上很多外部元件引起的阻抗失配。使用75微帶線以及與無源元件的接合焊盤尺寸相當的跡線寬度可以實現使阻抗失配降到最低的目標。使用第二接地基準就可以為連接到高針腳數FPGA的100差分跡線靈活選擇較細跡線寬度。務必使用75受控阻抗設計良好的BNC布局。建議在信號路徑上查找因布局結構變化引起的阻抗變化,并設計一種方式可以抵消過多電感或電容以保持目標特征阻抗值。通過遵循幾個簡單的布局指導原則,可以設計符合SDI高信號保真要求的板,并實現高密度連接至FPGA。本文引用地址:http://www.104case.com/article/191403.htm

評論