應對FPGA/SDI子系統中的高速板布局挑戰

簡介

電視和影院已經進入數字時代。視頻圖像曾以標準傳輸率(270Mb/s)傳輸,后來升級到高傳輸率(1.485Gb/s),現在已上升到3Gb/s。更高傳輸率實現了更高分辨率的娛樂圖像傳輸,但同時也使硬件工程師和物理布局設計師面臨著更大的挑戰。很多視頻系統都采用多功能FPGA和多傳輸率SDI集成電路,以支持高性能專業視頻在長距離的傳輸。FPGA需要高密度、細跡線寬度的傳輸,而高速模擬SDI傳輸需要阻抗匹配和信號保真。本論文概述了硬件工程師面臨的挑戰,并為處理這些挑戰提供了建議。

FPGA/SDI子系統

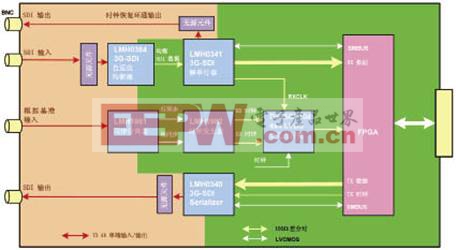

在典型的FPGA/SDI板中,數字視頻信號在BNC(卡拴式同軸接頭)與高性能SDI75跡線模擬集成電路之間傳輸。FPGA和SDI集成電路之間的互連包含通過FPGA細間距球柵發送的多對100差分信號。其中一個布局難點是75單端跡線和100差分跡線的共存。通常,這兩種跡線在元件所在頂層上傳輸。適合75的跡線寬度對于100跡線可能過寬。圖1是FPGA/SDI的示意框圖,顯示75和100的兩個區。

圖1 典型FPGA/SDI框圖

SDI布局難點

電影與電視工程師學會(SMPTE)發布了同軸電纜上數字視頻的傳輸標準。規定信號幅值為800mV±10%。必須通過芯片外的75±1%精確終端電阻器滿足此幅值要求。SMPTE標準還包含輸入和輸出的回波損耗要求,基本規定了輸入或輸出端口如何近似于75網絡。圖2顯示SMPTE對回波損耗的要求。

芯片外阻抗平衡網絡由電感器和并聯電阻器構成,通常用于抵消SDI集成電路的輸入或輸出電容。大交流耦合電容器(4.7µF)通常用于傳輸SDI串行位流,以避免低頻直流漂移。如圖3所示,75跡線的SDI集成電路及其BNC連接器之間附有多個芯片外無源元件。每個元件都具有串聯寄生電感,每個元件焊盤又具有并聯寄生電容,從而影響與75匹配的總阻抗。SDI布局的難點在于最大限度減少外部無源元件在75SDI端口造成的阻抗失配。

選擇FPGA/SDI子系統的板堆疊

應該使用什么跡線寬度 在小于3Gb/s的SDI速度中,銅損耗很小,并不構成選擇跡線寬度的重要考慮因素。選擇略小于元件接合焊盤的跡線寬度更為重要,以最大限度減少阻抗失配。0402尺寸的無源元件需要20密爾x25密爾的接合焊盤,以使15密爾到20密爾的跡線寬度最適合于75SDI跡線。

為了便于傳輸和偏斜匹配,FPGA的100差分信號使用細跡線寬度傳輸。寬松的耦合跡線通常用于避免較大的阻抗變化,而分支出的緊密耦合跡線則連接到終端電阻器或交流耦合電容器。

圖4顯示了適用于FPGA和SDI信號傳輸的板堆疊。在此堆疊中,SDI信號跡線采用在第4層以GND2為基準的75單端微帶線。GND2是在第4信號層形成的金屬島。第2和第3層的金屬(GND1和VCC面)在75跡線區被移除,以使其不會降低跡線的特征阻抗。FPGA的100差分跡線是在第2層以GND1為基準的寬松耦合微帶線。兩個接地基準(GND1和GND2)通過接地縫補鍍通孔相連。此板堆疊排列允許通過調節絕緣長度h2自由選擇75跡線的寬度,以及通過調節h1自由選擇100跡線的寬度。

評論