應(yīng)對(duì)FPGA/SDI子系統(tǒng)中的高速板布局挑戰(zhàn)

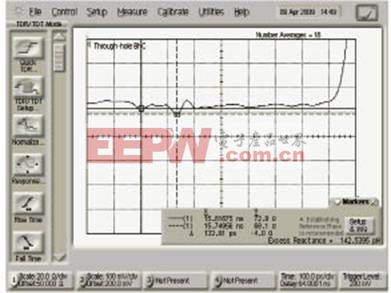

圖2 SDI端口和SMPTE限制值的輸入回波損耗圖

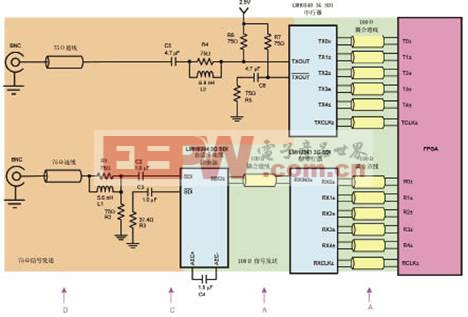

圖3 典型SDI電路(僅顯示高速信號(hào)路徑)

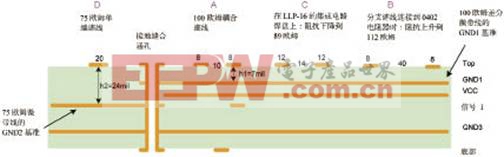

圖4 具有75和100跡線單獨(dú)接地參考的板堆疊

BNC連接器的布局

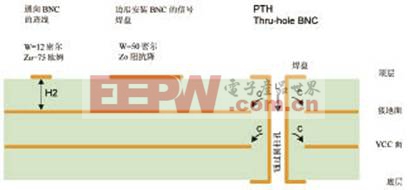

很多SDI板的常見問題是使用非優(yōu)化BNC連接器布局,因此產(chǎn)生嚴(yán)重的阻抗失配、無(wú)法滿足回波損耗要求,并削弱了設(shè)備的信號(hào)保真度。圖5顯示板的橫截面,其中12密爾寬的微帶線連接到50密爾寬的邊沿安裝BNC焊盤上。接地面被置于頂部跡線下的絕緣距離點(diǎn)上,以實(shí)現(xiàn)目標(biāo)跡線阻抗。連接器的接合焊盤是寬微帶線,因此焊盤的特征阻抗略低于跡線阻抗。焊盤具有較大的阻抗降,從而影響回波損耗和限制跡線的傳輸帶寬。

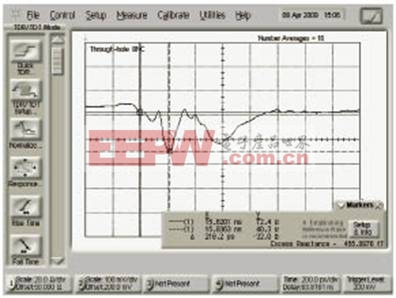

圖5還顯示了通孔BNC布局的橫截面。內(nèi)接地和供電面與鍍通孔絕緣,以避免短路。圓柱孔帶有一定的電感。每個(gè)接地或供電面的鍍通孔都具有寄生電容。小間隔的大鍍通孔將抑制容易造成大組抗降的多余電容。圖6顯示具有60密爾孔和20密爾間隔的設(shè)計(jì)不佳通孔BNC的阻抗形態(tài),圖中顯示了鍍通孔的阻抗從75跡線下降到40。

圖5 BNC布局的橫截面圖

圖6 設(shè)計(jì)不佳的通孔BNC的阻抗形態(tài)

設(shè)計(jì)良好的BNC布局

設(shè)計(jì)良好的BNC布局的目標(biāo)是避免BNC布局與連接到布局的跡線間產(chǎn)生過多的阻抗失配,可以遵循信號(hào)路徑查找板結(jié)構(gòu)變化可能導(dǎo)致的阻抗失配。時(shí)域反射計(jì)是能夠確定阻抗失配發(fā)生位置的儀器。可以使用電磁仿真器檢查板布局設(shè)計(jì)中的阻抗變化。如果阻抗過低,應(yīng)設(shè)計(jì)能夠抵消過多電容的板結(jié)構(gòu);如果阻抗過高,應(yīng)增加額外寄生電容使阻抗值接近目標(biāo)值。通過正確的電感和電容值,可以建立具有所需特征阻抗的通孔BNC布局。圖7顯示良好的通孔BNC布局示例,圖8顯示非常接近75目標(biāo)值布局的阻抗。

圖7 良好通孔BNC布局的頂視圖

圖8 良好通孔BNC布局的阻抗形態(tài)

FPGA/SDI板的布局指導(dǎo)原則

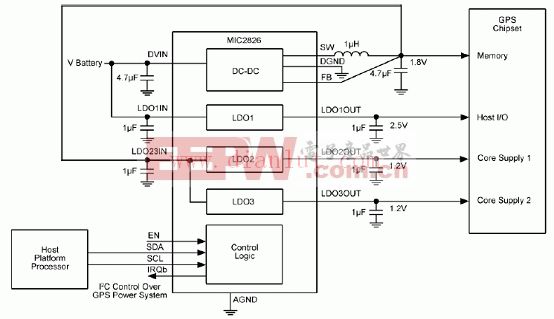

FPGA/SDI板的數(shù)據(jù)傳輸率低于3Gb/s,信號(hào)轉(zhuǎn)換時(shí)間約為100微微秒。SDI板布局的難點(diǎn)不在于速度,而在于計(jì)劃一種布局策略以最大限度減少與75SDI端口很多外部元件的阻抗失配,設(shè)計(jì)大BNC控制器的受控阻抗布局和實(shí)施支持75和100跡線的板堆疊。可以通過遵循以下這些簡(jiǎn)單的布局指導(dǎo)原則解決這些難點(diǎn):

評(píng)論