基于FPGA+DSP的雷達高速數據采集系統的實現

3.2 異步FIFO接口時序

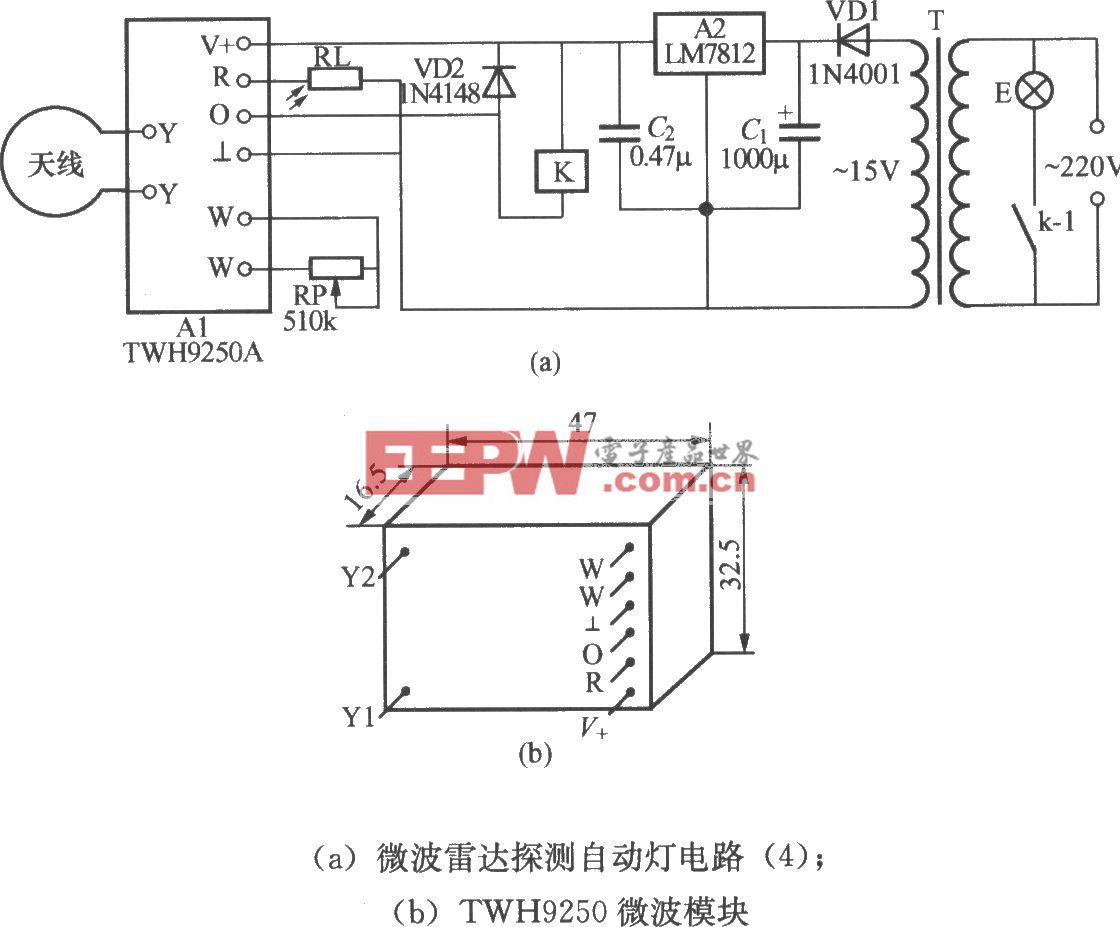

AD9235與FPGA接口設計應仔細考慮ADC轉換時鐘、FIFO寫時鐘及所選中間邏輯器件的時序和延時特性,以保證正確地設置采樣時鐘。AD-9235的采樣數據在延時7個采樣周期后出現在數據線上,圖4為A/D與FIFO接口時序。

圖4 A/D與FIFO接口時序

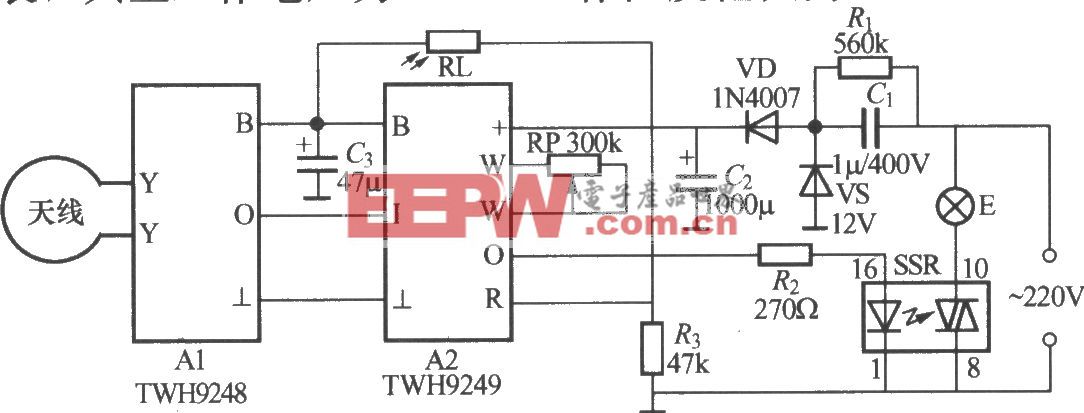

讀FIFO操作,利用EMIF外部存儲器的控制信號,包含有:輸出使能位和讀使能以及外部空間片選信號。讀寫時序如圖3,輸出使能和外部空間片選信號低時,異步FIFO讀使能RD_EN有效,當讀使能位為低時,待讀出的數據進行初始化,隨后會跳變為高電平,異步RD_CLK端產生上升沿,此時異步FIFO中數據被讀出。圖1中的HALF_FULL位直接與TMS320C6201外部存儲區域中斷EXT-INT5觸發連接,當FIFO緩存達到半滿時,上升沿觸發DSP外部中斷,DSP啟動DMA(直接數據存儲)以突發方式讀取FIFO數據,在時鐘CLOCKOUT1下讀取FIFO存儲數據。EMIF與FIFO的讀邏輯關系為;。

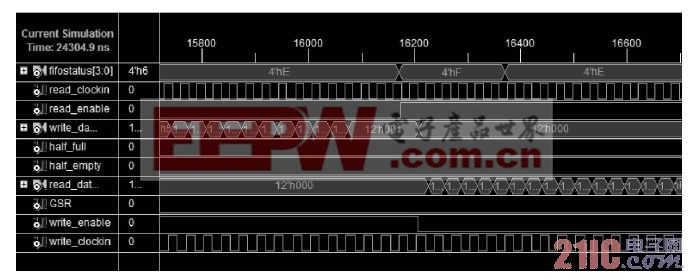

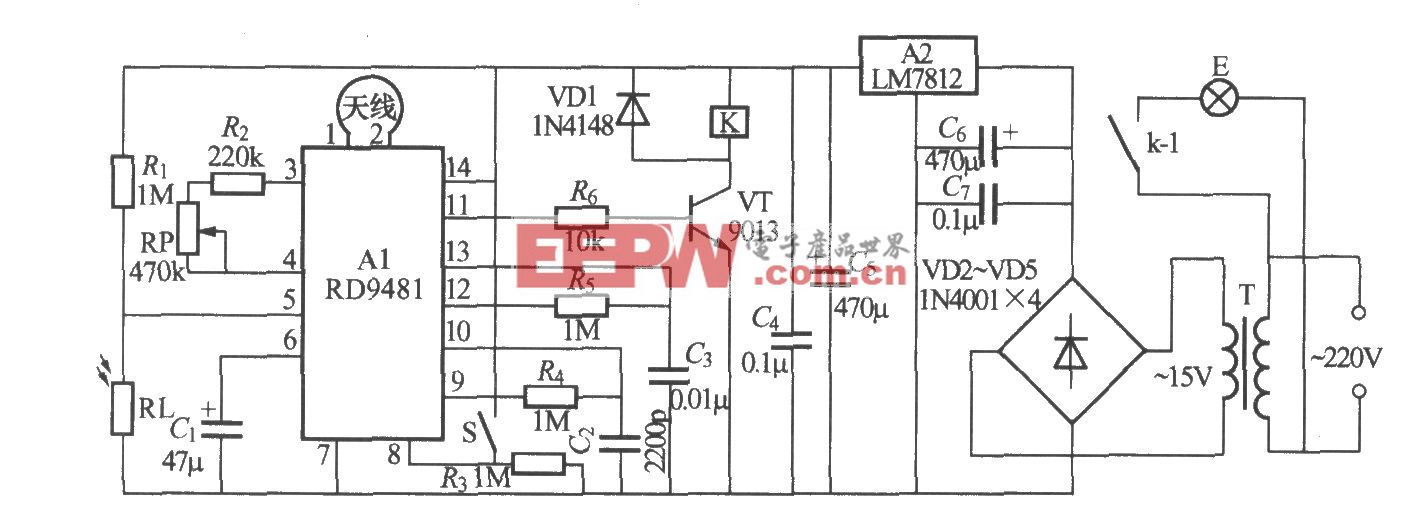

圖5為異步FIFO仿真圖,輸入數據寬度12位,輸出數據寬度為24位。讀時鐘為50置MHz,寫時鐘為30 MHz。

和讀使能

和讀使能 以及外部空間片選信號

以及外部空間片選信號 。讀寫時序如圖3,輸出使能

。讀寫時序如圖3,輸出使能 和外部空間片選信號

和外部空間片選信號 低時,異步FIFO讀使能RD_EN有效,當讀使能位

低時,異步FIFO讀使能RD_EN有效,當讀使能位 為低時,待讀出的數據進行初始化,隨后會跳變為高電平,異步RD_CLK端產生上升沿,此時異步FIFO中數據被讀出。圖1中的HALF_FULL位直接與TMS320C6201外部存儲區域中斷EXT-INT5觸發連接,當FIFO緩存達到半滿時,上升沿觸發DSP外部中斷,DSP啟動DMA(直接數據存儲)以突發方式讀取FIFO數據,在時鐘CLOCKOUT1下讀取FIFO存儲數據。EMIF與FIFO的讀邏輯關系為

為低時,待讀出的數據進行初始化,隨后會跳變為高電平,異步RD_CLK端產生上升沿,此時異步FIFO中數據被讀出。圖1中的HALF_FULL位直接與TMS320C6201外部存儲區域中斷EXT-INT5觸發連接,當FIFO緩存達到半滿時,上升沿觸發DSP外部中斷,DSP啟動DMA(直接數據存儲)以突發方式讀取FIFO數據,在時鐘CLOCKOUT1下讀取FIFO存儲數據。EMIF與FIFO的讀邏輯關系為 ;

; 。

。

圖5為異步FIFO仿真圖,輸入數據寬度12位,輸出數據寬度為24位。讀時鐘為50置MHz,寫時鐘為30 MHz。

圖5 異步FIFO仿真圖

4 設計應注意問題

若用異步FIFO中的FULL信號作為中斷源,滿信號位FULL有效,觸發DMA開始傳輸,在滿信號和DMA傳輸之間,A/D采集時鐘仍然驅動A/D轉換器,會覆蓋之前存儲的采集數據,造成數據丟失;若采用HALF-FULL信號作信號標志位,半滿時候,開始DMA傳輸,不用中斷數據采集,由于A/D寫入速度低于EMIF讀出速度,也不會造成數據覆蓋。

FPGA內部的異步FIFO數據總線與TMS320C6201的數據總線相連,應注意數據采集與TMS320C6201訪問外設間的總線沖突。應保證沒有長時間占用數據總線的外部設備,否則造成采集數據丟失。

5 結論

針對雷達的回波信號,設計基于FPGA與DSP的高速數據采集系統,介紹了雷達前端信號A/D外圍轉換電路,利用DCM和異步FIFO實現ADC與高速DSP間的數據緩沖,以保證采集數據的有效傳輸。系統采樣率為30 MHz,采樣精度為12位,異步存儲緩沖FIFO大小為6 kbits,能較好地滿足高速采集要求。FIFO與DSP采用24位數據接口,讀取FIFO采用DMA數據傳輸,較充分利用DSP資源,提高了系統實時處理的能力。

評論