基于FPGA的高速數據處理系統設計

2.2 仿真實驗結果

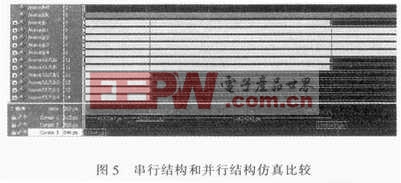

為了比較串行結構和并行結構的計算速度,在Xilinx 7.1ISE平臺中(Virtex-4器件的最低版本要求),選用Virtex-4系列的XC4VSX25器件,用Verilog HDL語言設計串行結構和并行結構,并在ModelSim中對兩種結構進行仿真比較。由于仿真時間長度的限制,采用5位128長度的三角波模擬采集到數據,并將XtremeDSP? Slice的計算速率設定在250 M/s,仿真波形結果如圖5所示。本文引用地址:http://www.104case.com/article/191296.htm

從圖5中可看出,采用串行結構,計算耗時約為15.8 ms,而采用4個XtremeDSP Slice的并行計算結構,計算耗時約為4.2 ms。從仿真結果的比較可知,串行結構耗時約為并行結構的4倍。因此,在本系統中并型結構的計算速度是正比于并行度的,這與理論上并行計算可以成倍減少計算時間的分析一致。

3 結束語

通過以XC4VSX25為核心的嵌入式系統,實現數據采集、數據存儲、LCD顯示、USB數據傳輸和數據處理,完成光纖微擾動傳感的擾動識別和定位功能,具有高速、實時、低成本、高靈活性的優點。本系統利用系統內特有的硬件結構XtremeDSP Slice實現高效高速的數據處理,同時在ISE軟件中XtremeDSP Slice以IP核形式使用,無需自己構造乘法器和加法器,既節省了大量FPGA資源又大大減少開發難度。通過仿真比較可以看出,本系統中并型結構的計算速度是正比于并行度的,因此可以通過提高并行度來提高系統的計算速度,滿足高速實時的數據處理要求。

干涉儀相關文章:干涉儀原理

評論