基于FPGA的跳擴頻信號發送系統設計

對部隊中已大量裝備使用的跳擴頻電臺的維護與測試需要性能穩定的跳擴頻信號源,因此非常必要研制使用方便、性能可靠的跳擴頻信號源,以解決部隊急需,從而提高部隊的機務維修保障能力。隨著電子技術的發展,尤其是近十年來數字化技術、超大規模集成電路和軟件方面的新技術新成果不斷涌現,使得設計高可靠、高精度、高穩定可攜帶方便的測試系統成為可能。與傳統測試系統中的跳擴頻信號源相比,本跳擴頻信號發送系統采用了FPGA、DDS等多種先進技術,具有體積小、重量輕、成本低、集成度高、精度高、可靠性強等優點,能夠有效地模擬產生需要的跳擴頻信號,為機載跳擴頻電臺的測試提供可靠的激勵信號。

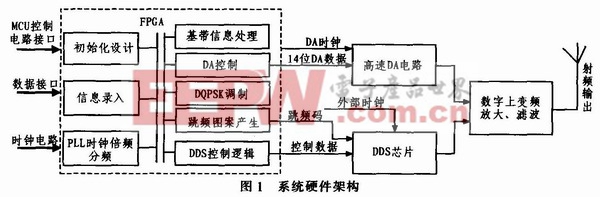

1 系統設計總體方案

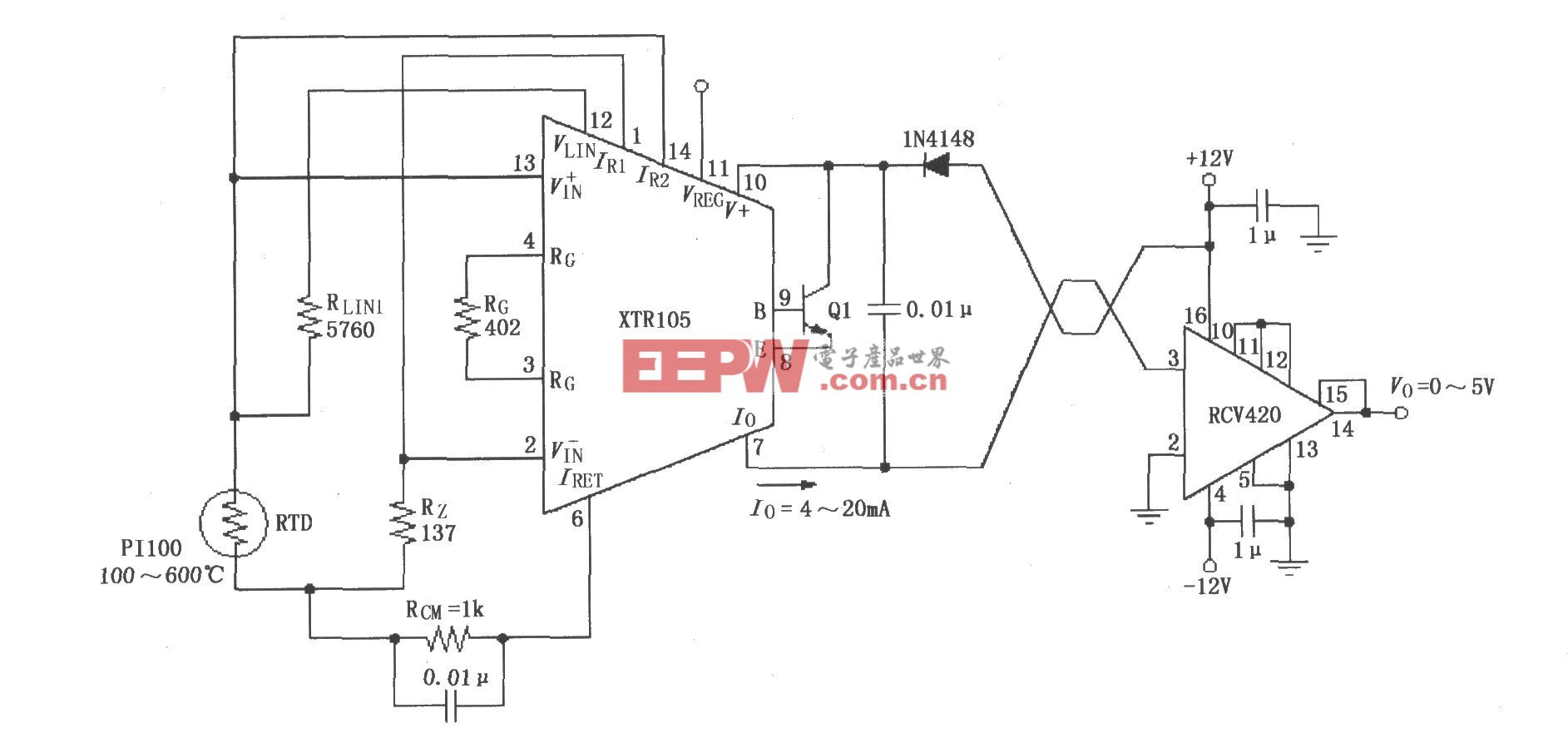

針對信號源需求分析,設計系統總體方案如圖1所示。FPGA接收主控單元(MCU)傳遞的信息數據,接收數據源速率為4.8 kb/s。基帶處理部分進行差錯編碼,編碼處理后的基帶信息數據以9.6 kb/s信息速率輸入成幀電路,組幀后信息速率為38.4kb/s。中頻處理電路接收38.4 kb/s信息速率的數據,并進行擴頻和DQPSK調制。擴頻調制PN碼碼片速率為1.228 8 M碼片/秒,即每個調制符號對應64個碼片。系統中頻輸出8.192 MHz DQPSK數字數據。系統帶寬跨度為UHF(超短波)105~156 MHz,分了16個跳頻點帶寬≥45.5MHz。跳頻最小間隔≥2.5 MHz,跳頻速度1 000 Hop/s。

2 關鍵模塊研究與實現

2.1 DQPSK調制

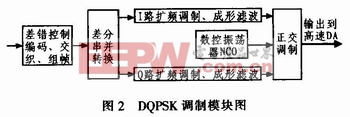

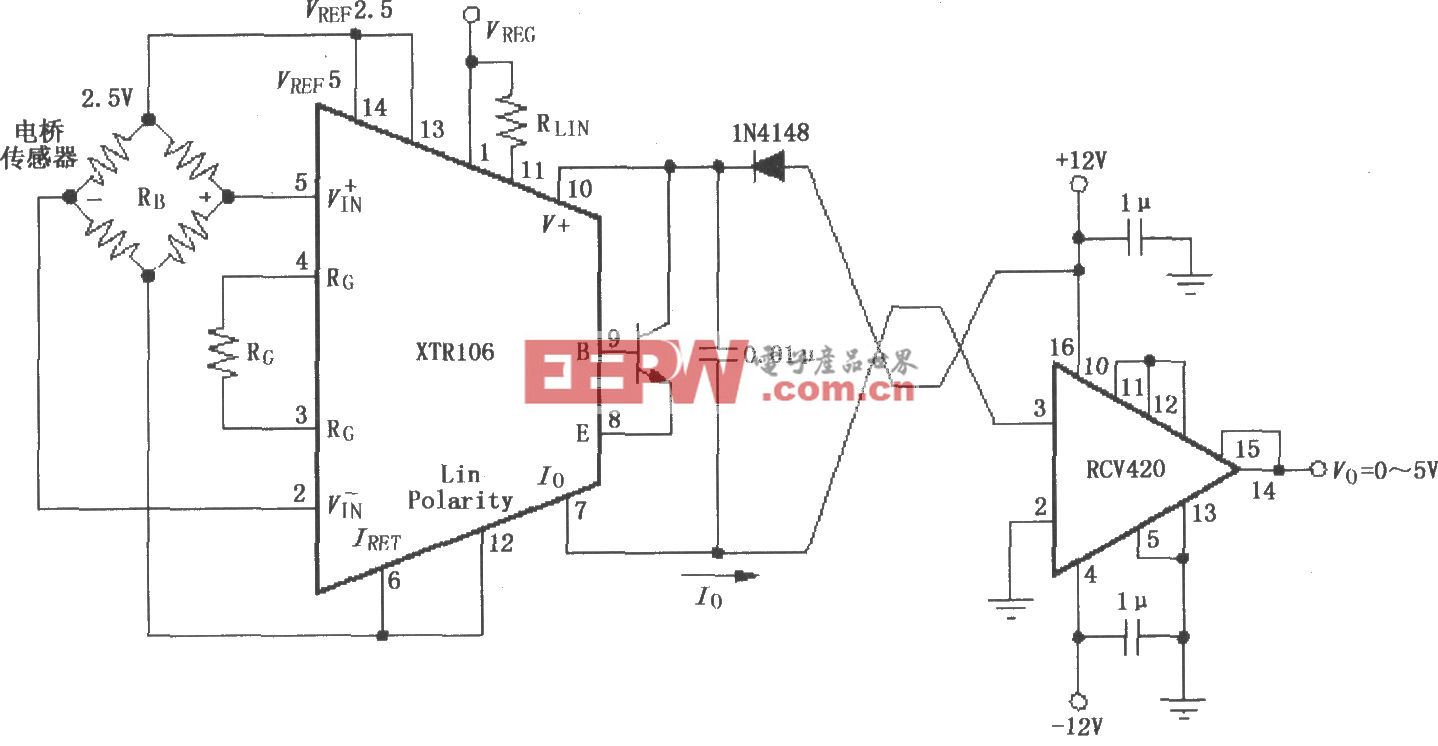

中頻調制使用數字化DQPSK(相對相移鍵控)調制,該調制技術能有效利用數據帶寬,同時采用差分編碼解決QPSK調制時出現的相位模糊問題,保證了數據的正確解調。DQPSK調制框圖如圖2所示。

差錯控制編碼采用(217)卷積編碼,碼率為1/2。交織采用塊交織,交織器長度為384,即一大幀的長度。為保證數據的連續發送,交織采用兩個交織器輪流工作。交織后數據以9.6 kb/s交給DQPSK調制,經差分串并轉換,以64位碼長的M序列對轉換后碼率減半的數據進行擴頻調制和成形濾波。數控振蕩器(NCO)產生正交調制的波形,對成形濾波后的信號進行正交調制。

2.1.1 濾波成形

DOPSK調制后的信號存在以下問題:調制后的信號將出現瞬時變化,這將不可避免地導致信號的瞬時頻譜的擴散,如果無失真地傳輸該信號就要求有很寬的信道帶寬,這在信號傳輸中是無法實現,唯一有效的途徑就是采用濾波技術限制頻譜,這就需要基帶濾波。基帶濾波是在時域上擴展符號,如果設計的不好,在接收端將會引起嚴重的碼間干擾(ISI)。無碼間擾準則可表示為:

![]()

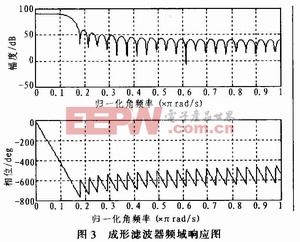

平方根升余弦滾降濾波器有一個平滑的過渡帶,通過引入滾降系數來改變傳輸信號的成形波形,可以減少抽樣定時脈沖誤差所帶來的影響。本設計中采用56階,滾降系數為0.35的平方根升余弦濾波器,每個符號抽樣8個點。系統中所設計的成形濾波器頻域響應如圖3所示。

評論