基于FPGA的高速數據處理系統設計

2 數據處理設計

2.1 數據處理結構

本系統的數據處理結構如圖3所示,首先是采集一定長度的信號存儲到雙口RAM中,然后經過擾動識別決定是否需要進行擾動定位計算。由于擾動識別和定位計算需要將采集到的數據保存到數據處理完畢,所以FPGA中的雙口RAM要有足夠的空間,在數據處理的同時繼續存儲采集到的數據。而在工作時,由于采用了高速的AD7356,最高采樣速率可以達到5 M/s,所以要求擾動識別和定位計算速度足夠快。本文引用地址:http://www.104case.com/article/191296.htm

擾動識別部分由于采用的是平方后積分并與閾值比較的模式,屬于順序計算,耗時不多,數據處理耗時的主要部分是擾動定位計算。擾動定位計算采用的是相關計算,其所消耗的時間在計算速度固定時,由數據長度L和相關長度(移位次數)n決定。進行一次相關計算的計算量為Ln次乘法和(L-1)n次加法。

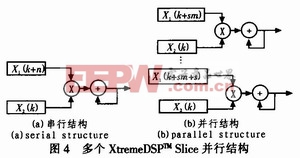

在FPGA數據處理方面,當資源成本為主要制約時,根據速度要求,采用串行結構實現或DA結構實現;當速度成為主要制約時,則根據資源成本因素,采用并行結構實現或DA結構實現。而DA結構主要是通過對資源合理的利用來減小資源的空閑時間,從而提高系統的速度。但是對于本系統,在計算過程中各資源幾乎是在全速運行,DA結構并不能提高系統的速度,所以需通過并行結構(圖4)來提高系統運行速度。通過圖4可以看出,如果采用串行結構,整個相關計算由1個XtremeDSP Slice(或者1個單核處理器)完成,每完成一次互相關運算,整個數據段移位一次,共移位n次。因此為了及時處理采集到的數據,串行結構的計算速度至少是采集速度的n倍(根據傳感長度不同,n最大可達2 500)。而AD7356最高采樣速率可以達到5 M/s,因此計算速度過快,單個XtremeDSP Slice不可能完成。而如果采用s個XtremeDSP Slice并行結構,則一次互相關計算相當于串行結構時的s次互相關計算,而本來需要移位n次完成的計算,現在只需要m(圖4中變量m=n/s)次移位,每次移位s,即可完成。因此,每個XtremeDSP Slice的計算速度為采集速度的m倍,可以有效減少對計算速度的要求。

干涉儀相關文章:干涉儀原理

評論