基于FPGA的跳擴頻信號發送系統設計

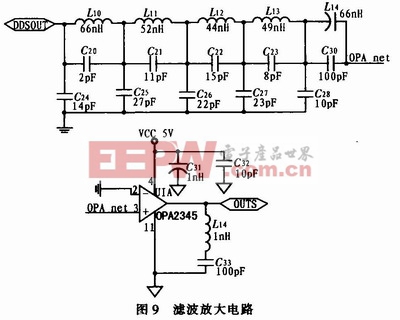

2.3.4 濾波放大電路

針對相位舍位誤差造成的雜散、幅度量化誤差造成的雜散和DAC非理想特性造成的雜散等3個主要諧波干擾源。且考慮到濾波緩沖放大電路與已有的DDS的PCB板之間的電路的接口可能會帶來較大的干擾,必須對AD9951輸出頻率進行濾波處理。橢圓型濾波器在通帶內和阻帶內都有等波紋的起伏,比巴特沃斯和切比雪夫有更陡的下降梯度,過渡帶陡峭,在相同性能指標下,橢圓濾波器所需的階數更小。設計借助Mult-isim 10.1高頻電路仿真軟件設計了9階橢圓低通濾波電路,截至頻率為160 MHz,通帶內的衰減低于0.2 dB。本文引用地址:http://www.104case.com/article/191295.htm

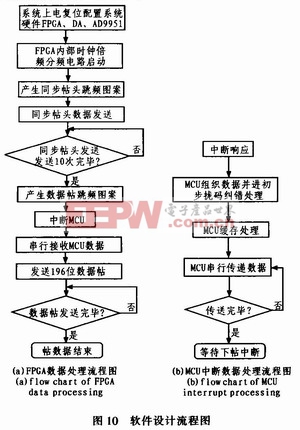

3 軟件設計

根據系統需求,采用QuartusⅡ8.0開發平臺,使用VHDL語言編寫FPGA器件執行程序,軟件設計流程如圖10所示。系統上電復位,等待MCU啟動發送信號,各個模塊配置完成,選擇同步發送時鐘,等待同步幀頭發送,同步幀頭以每秒鐘400跳的速率發送10次,同步幀頭發送完畢,選擇正常數據發送時鐘并向MCU產生中斷,從MCU緩存中索取數據,MCU將數據傳遞給FPGA進行基帶處理和中頻調制。

MCU中斷處理,MCU接收FPGA發出的中斷信號,將迅速響應中斷,并組織數據為一大幀,進行初級糾錯處理后,存入緩存,以備FPGA從MCU緩存中取數據,保證了中頻調制數據的連續性。

4 結束語

依據跳擴頻通信信號的需求,設計了以FPGA和DDS為架構,用VHDL語言編程實現的跳擴頻信號發送系統,該系統能以連續的4.8 Kb/s的速率、在108~155.975 MHz范圍內寬間隔跳頻發送數據。本設計的主要優點是采用了軟件無線電技術,使用高速、高穩定性和高可靠性的集成芯片,體積小重量輕,性價比高。實驗結果證明,該跳頻信號發送系統可在其外部參數可控的情況下,穩定地傳送全頻段跳頻信號,具有較高的應用價值。

評論