基于FPGA的高性能DAC芯片測試與研究

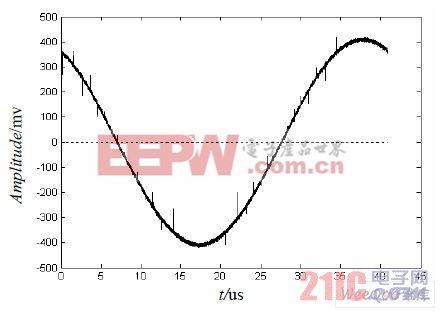

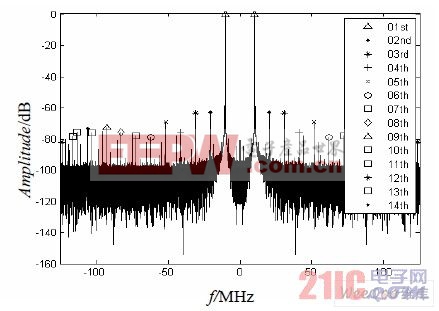

Sin 信號測試:輸入正弦波頻率25 kHz,AD 采樣率為100 MHz/s,輸出數字信號經過Matlab 分析計算后,測得SNR是58 dB,SINAD 是57.75 dB,SFDR 是62.84 dB,THD 是58.62 dB,ENOB 是9.3 位。時域波形和FFT 變換后14 階諧波的頻譜如圖4 和圖5 所示。

圖4 sin 信號輸出時域波形

圖5 sin 信號輸出頻域波形

4 結語

以12 位、250 Ms/s DAC 芯片為例,在FPGA 的基礎上使用回路測試法,測試了其靜態特性參數和動態特性參數。實驗結果表明,可以有效地測試DAC 芯片的靜態特性參數和動態特性參數。同時可以測試不同分辨率和采樣速度的DAC 芯片,測試結果比普通模擬測試儀器的精度高,測試系統比專用DAC 自動測試設備成本低。

評論