基于FPGA的高性能DAC芯片測試與研究

D/A 轉換器作為連接數字系統與模擬系統的橋梁,不僅要求快速、靈敏,而且線性誤差、信噪比和增益誤差等也要滿足系統的要求[1]。因此,研究DAC 芯片的測試方法,對高速、高分辨率DAC 芯片的研發具有十分重要的意義。

本文引用地址:http://www.104case.com/article/191290.htm目前,波形測量和分析協會已提出了DAC 測試的技術標準IEEE Std.1057,里面的術語和測試方法為DAC 測試提供了更多的參考。傳統的標準測試只適于信號發生器、示波器等測試儀器,但是測試精度不高;大規模芯片測試時則使用自動測試設備(ATE),但是成本很高;最近提出的DAC 的測試方法,比如結合V777 數字測試系統可以進行DAC 測試,應用模擬濾波器進行音頻DAC 測試,利用數模混合信號測試系統Quartet 對高速DAC 進行測試,等等[5],這些方法在通用性、精確度和成本方面無法同時滿足。為了達到上述要求,提出了基于FPGA 的高性能DAC 芯片回路測試法。

1 DAC 主要技術參數

DAC 的主要技術參數基本上可以分為靜態特性參數和動態特性參數。DAC 的靜態特性參數用來確定其轉換的精確度,主要包括失調誤差(Offset Error)、增益誤差(Gain Error)、積分非線性誤差(INL)以及微分非線性誤差(DNL)等。DAC動態特性參數用來確定其交流條件下的性能,主要包括信噪比(SNR)、信號噪聲和失真比(SINAD)、有效位數(ENOB)、總諧波失真(THD),以及無雜散動態范圍(SFDR)等。

2 測試方案

2.1 設計原理

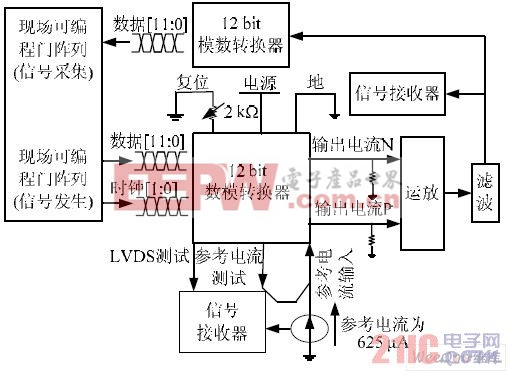

DAC 芯片參數回路測試法,就是將待測信號形成一個完整的信號回路。首先,使用FPGA 產生待測信號,經過DAC芯片后轉換成模擬信號,再經過濾波、放大電路和ADC 芯片轉換成數字信號,存儲在FPGA 的RAM 里,然后使用QuartusII 軟件Signal tap II 工具取出數據,導入Matlab 軟件后,就可以對數字信號進行分析和計算,從而得到DAC 的技術參數[6]。在ADC 采樣之前使用模擬信號接收器,如示波器、頻譜儀等,可與后端測試結果比較分析。設計原理如圖1 所示。

由于FPGA 使用非常靈活,通過配置不同的編程數據可以產生不同的電路功能,對于不同分辨率和采樣速度的DAC芯片都可以進行參數測試;濾波和運算放大電路盡可能地降低信號在轉換和傳遞過程中的噪聲;數字信號在分析和計算方面比模擬信號更加準確,保證了測試系統的精確度;相對于其他DAC 測試系統來說,本測試方案使用的元器件比較少,成本比較低。

圖1 設計原理

2.2 硬件實現

DAC 使用12 位分辨率、250 Ms/s 采樣速度的DAC 芯片,芯片采用LVDS 差分電路、PTAT 基準源以及4+4+4 電流源陣列等關鍵技術設計,可以滿足高速高分辨率轉換電路處理的要求。FPGA 是Altera 公司Cyclone III 系列EP3C25Q240C8 芯片,功耗小,系統綜合能力強,價格較低,包含了24*個邏輯單元、594 Kbit 內存空間和4 個鎖相環,硬件資源完全可以滿足測試的要求[8] 。ADC 是LINEAR 公司的LTC2242-12 芯片,交流特性非常好,降低了測試系統帶來的誤差。運算放大器是ADI 公司的AD8008 芯片,非常好的驅動特性保證了DAC 芯片輸出信號的質量,提高了DAC 的驅動能力。

評論