基于FPGA的IEEE 1394b高速數據傳輸系統

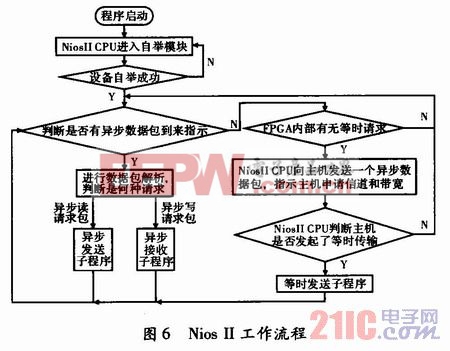

本系統中Nios II主要完成3個功能:(1)實現1394b設備的自舉,協助主機完成設備識別以及設備的身份確認。(2)實現異步數據收發功能,異步讀、異步寫,根據請求包的類型進行分別處理。(3)滿足傳輸條件時,為等時傳輸申請等時信道和帶寬,成功后開始組織等時傳輸,傳輸結束后釋放信道和帶寬。圖6為Nios II工作流程圖。本文引用地址:http://www.104case.com/article/191244.htm

下面介紹等時傳輸過程,根據系統設計,將外部DVD壓縮圖像數據作為等時數據來處理。具體過程如下:

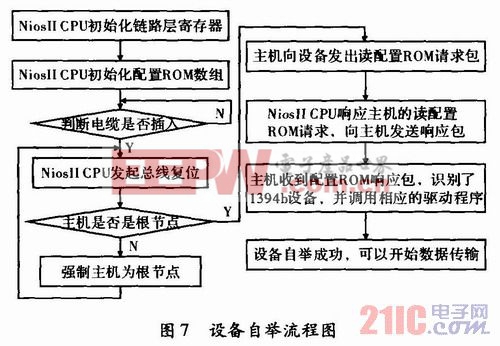

(1)NioslI CPU對1394b的OHCI和鏈路層寄存器進行初始化,判斷線纜是否插入,強制根節點,直到設備完成自舉,節點的身份確認,如圖7所示。

(2)自舉過程結束后,Nios II CPU檢測等時傳輸的條件是否滿足,如果滿足則向主機發出申請,申請等時信道和帶寬。

(3)申請成功后,Nios II CPU開始組織數據進行傳輸。首先它向DMA控制器發送寄存器配置信息,從而將數據傳送任務交由DMA控制器完成。

(4)DMA控制器從FPGA的緩存單元中取出數據,并添加包頭將數據拼接成合法的等時數據包格式,并發起PCI主模式傳輸。

(5)數據經由PCI總線傳送到鏈路層芯片中,又通過物理層芯片傳送到1394b總線上,并由主機上連接的數據采集卡接收,最終由主機端的應用程序解壓縮和播放數據。

3 結束語

文中介紹了一種基于FPGA的IEEE 1394b高速數據傳輸系統,它能實現外部多路數據的實時傳送。由于支持1394b的設備與支持1394a的設備可以相互兼容,所以在此基礎上可以建立1394組網平臺,實現多個系統的互聯與傳輸。

評論