基于FPGA的IEEE 1394b高速數(shù)據(jù)傳輸系統(tǒng)

當(dāng)FPGA為PCI主設(shè)備時(shí),它通過PCI-Avalon橋發(fā)起PCI主傳輸,如圖3所示是PCI主模式寫交易的仿真時(shí)序。當(dāng)FPGA為PCI從設(shè)備時(shí),鏈路層控制器是PCI命令的發(fā)起者,并由PCI-Avalon橋自動(dòng)進(jìn)行分析,將PCI總線上的命令轉(zhuǎn)化為相應(yīng)的Avalon總線信息,圖4所示是PCI從模式配置讀寫仿真圖。本文引用地址:http://www.104case.com/article/191244.htm

2 嵌入式軟核Nios ll的設(shè)計(jì)

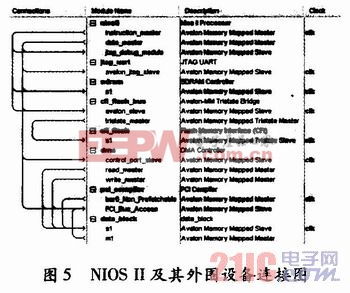

Nios II是Ahera推出的32位RSIC嵌入式處理器,根據(jù)用戶的需求有Nios II/f(快速)、Nios II/s(標(biāo)準(zhǔn))以及Nios II/e(經(jīng)濟(jì))3種可配置的方案。Nios II還支持片內(nèi)調(diào)試和指令定制,具有較大的靈活性和可擴(kuò)展性,而且許多常用的標(biāo)準(zhǔn)外設(shè)接口已經(jīng)以IP核的形式集成在了SOPC Builder開發(fā)環(huán)境中,用戶如需要?jiǎng)t可直接調(diào)用,縮短了開發(fā)周期和成本。根據(jù)應(yīng)用需要,本系統(tǒng)將Nios II配置成快速型,時(shí)鐘頻率為100 MHz。Nios II與各種外設(shè)通過Avalon總線連接,具體的連接關(guān)系如圖5所示。

評論