基于1553B總線協議的解碼器設計和FPGA實現

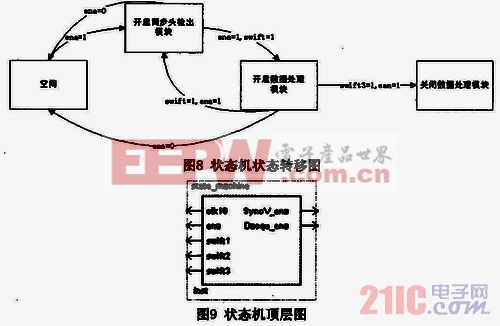

狀態機模塊是要正確地協調工作同步頭檢出模塊和數據處理模塊,如圖8所示狀態機模塊的狀態轉移圖。當狀態機被使能時,說明1553B總線數據來臨,此時狀態機產生SyncV end信號告訴同步頭檢出模塊開始工作。當同步頭檢出模塊工作結束時,產生Sync ready信號,告訴狀態機要開啟數據處理模快。當數據處理模塊工作到一定時間時會產生一個sync head信號,這個信號的意義是要讓狀態機告訴同步頭檢出模塊開始檢測下一個字的同步頭。而此時數據處理模塊還沒有工作完,只有當數據處理模塊產生finish信號時,才表示數據處理模塊工作完成,告訴狀態機關閉數據處理模塊。圖9所示是狀態機頂層圖。本文引用地址:http://www.104case.com/article/191237.htm

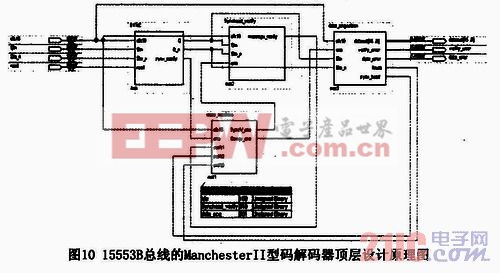

在QuartuslI中的原理圖輸入界面中,將以上各模塊正確地連接在一起,如圖10所示為1553B總線的manchesterII型碼解碼器的頂層設計原理圖。

3 時序約束與驗證

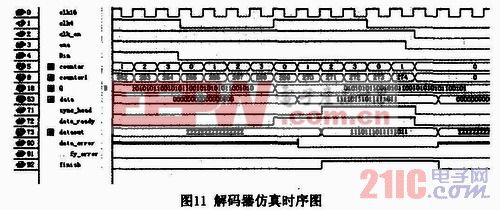

時序約束是FPGA設計中非常重要的環節,只有建立了合理的時序約束,設計才能正常地工作。如今的FPGA中一般都有全銅層的全局時鐘驅動網絡,本設計中16MHz的時鐘設置成全局時鐘,可以有效地避免這些時鐘信號到達各寄存器時鐘短的時鐘偏斜。將時鐘的最高頻率設置成16.8MHz。圖11所示為解碼器的仿真時序圖,解碼器在一個字周期之后,解碼出數據為1110111011111011。

文章詳細介紹了一種利用FPGA實現的1553B總線用的ManchesterlI型碼解碼器,文章給出了解碼器各模塊的功能和實現方法,最后給出了頂層設計原理圖。給出的仿真時序圖證明這是一種可靠的實現方法。

評論