基于1553B總線協(xié)議的解碼器設(shè)計和FPGA實現(xiàn)

2 EDA設(shè)計

本文設(shè)計的ManchesterII型碼解碼器選擇ALTERA公司的Cyclone系列的EPlC6Q240C6芯片作為目標器件,在QuartusII9.0集成環(huán)境中,使用Verilog HDL硬件描述語言和原理圖混合輸入方法實現(xiàn),使設(shè)計簡潔有效。

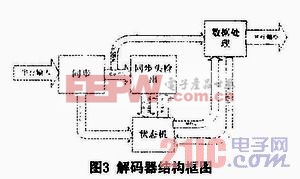

解碼器的功能是將1553B總線中串行輸入的數(shù)據(jù)轉(zhuǎn)變成并行數(shù)據(jù),并檢查數(shù)據(jù)和奇偶校驗位是否正確,為下游的1553B處理器提供正確的數(shù)據(jù)。如圖3所示,解碼器包括同步模塊、同步頭檢出模塊、數(shù)據(jù)處理模塊、狀態(tài)機模塊。設(shè)計采用16M時鐘的工作頻率。本文引用地址:http://www.104case.com/article/191237.htm

數(shù)據(jù)信號和使能信號可以在時鐘信號的一個周期之內(nèi)的任意時間來領(lǐng),也就是說無法定位數(shù)據(jù)信號和使能信號對于時鐘信號上升沿的時間間隔,這將使各模塊內(nèi)部的時鐘計數(shù)器無法準確地計時,使狀態(tài)機無法準確地進行狀態(tài)跳變。

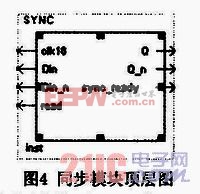

同步模塊的作用相當于一個D觸發(fā)器,它可以使數(shù)據(jù)信號和使能信號相對于時鐘信號的上升沿有固定的時間間隔,這個時間間隔就是同步模塊的tco,即時鐘輸出延時。這樣就為下游模塊的時鐘計算和時序約束提供了一個固定的參數(shù),為各模塊的時鐘計數(shù)器準確計時和狀態(tài)機正確跳變奠定了基礎(chǔ)。

如圖4所示,同步模塊中Din和Din_n管腳(Din_n為Din的方向輸入信號)接收來自1553B模擬收發(fā)器的數(shù)據(jù)信號,read管腳接收模擬收發(fā)器發(fā)出的使能信號。產(chǎn)生與16MHz時鐘的上升沿同步的數(shù)據(jù)信號和使能信號。

評論